## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PARIS VI

Spécialité Informatique

## Présentée par Yannick DUMONTEIX

Pour obtenir le grade de

### Docteur de L'Université Paris VI

# OPTIMISATIONS DES CHEMINS DE DONNÉES ARITHMÉTIQUES PAR L'UTILISATION DE PLUSIEURS SYSTÈMES DE NUMÉRATION

Soutenue le 10 octobre 2001, devant le jury composé de :

Alain Guyot Rapporteur

Marc Daumas Rapporteur

Michel Robert Examinateur

Jean-Marie Chesneaux Examinateur

Alain Greiner Examinateur

Habib Mehrez Directeur de thèse

À Fabienne, à Cassandre et Andreas, à eux et à tous ceux pour qui j'ai de l'affection.

« Entre

ce que je pense,

ce que je veux dire,

ce que je crois dire,

ce que je dis,

ce que vous avez envie d'entendre,

ce que vous croyez entendre,

ce que vous entendez,

ce que vous avez envie de comprendre,

ce que vous comprenez,

il y a dix possibilités qu'on ait des difficultés à communiquer.

Mais essayons quand même ... »

Le père de nos pères et L'encyclopédie du savoir relatif et absolu Bernard Werber

## **Avant-Propos**

Je souhaite exprimer toute ma reconnaissance au professeur Alain GREINER, pour m'avoir accueilli au sein du thème ASIM du laboratoire LIP6 de l'université Pierre et Marie Curie, et pour l'intérêt qu'il a porté au déroulement de mes travaux.

Je remercie le professeur Habib MEHREZ de l'université Pierre et Marie Curie, d'avoir dirigé mes recherches, et de son aide durant la rédaction de ce mémoire. Je tiens également à lui exprimer ma gratitude pour la confiance et l'amitié qu'il m'a témoignées ainsi que pour sa gentillesse légendaire.

Je tiens à remercier monsieur Alain GUYOT, maître de conférence à l'institut National Polytechnique de Grenoble et monsieur Marc DAUMAS, chargé de recherches au CNRS à l'École Normale Supérieure de Lyon, pour l'honneur qu'ils m'ont fait en acceptant de participer au jury de cette thèse, et pour le soin qu'ils ont apporté à l'examen de ce document.

De même je tiens à remercier monsieur Michel ROBERT, professeur au Laboratoire d'Informatique, de Robotique et de Microélectronique de l'université de Montpellier II, le professeur Jean-Marie Chesneaux Directeur des études à l'Institut de Sciences et Technologie de l'Université Pierre et Marie Curie, et de nouveau le professeur Alain GREINER, d'avoir accepté d'être examinateurs de cette thèse.

Je profite de cette occasion pour témoigner ma reconnaissance à l'ensemble des personnes qui ont contribué de près ou de loin à mes travaux de thèse, tout spécialement à Nicolas VAU-CHER, à Frédéric PÉTROT et Ludovic JACOMME pour leurs compétences multiples, et à Roselyne CHOTIN et Arnaud MONTREUIL, anciens étudiants du DEA ASIME, dont les stages m'ont été précieux.

Je remercie aussi tous les membres du pôle ASIM du Laboratoire LIP6 pour leur sympathie et particulièrement Mademoiselle Marie-Catherine HURGUES et Messieurs Yann BAJOT, Joachim PISTORIUS, Mourad ABERBOUR, Cyril SPASEVSKI, Hassan ABOUSHADY, Olivier GLUCK, Walid MAROUFI, Arnaud CARRON, Mounir BEN ABDENBI, Grégoire AVOT et Fabrice ILPONSE pour leurs conseils, aides et amitié pendant toutes ces dernières années.

## Résumé

Cette thèse présente l'intégration de nouveaux systèmes de représentations des nombres, plus précisément les systèmes de notations redondantes, dans le flot de conception de cœurs de calculs. Les travaux effectués se découpent en trois phases.

La première est consacrée à l'introduction des systèmes de notations redondantes aux côtés des systèmes de notations classiques. À cet effet nous avons défini une nouvelle arithmétique qualifiée de *mixte*. Celle-ci répond aux problèmes liés à l'usage simultané des notations classiques et redondantes. Elle a donné lieu au développement de nouveaux opérateurs très performants capables de tenir compte de toutes les combinaisons de notations classiques/redondantes sur leurs entrées/sorties. Les trois opérations élémentaires que sont l'addition, la somme et la multiplication, ont été étudiées. Nous distinguons le cas particulier de l'ajout de deux opérandes (addition) du cas général de l'ajout de trois opérandes et plus (somme). Ces diverses opérations ont été réalisées sous formes de générateurs où la taille, le signe et la notation de chacune des opérandes ainsi que l'algorithme de calcul utilisé sont paramétrables.

La deuxième phase a eut pour objectif de déterminer l'impact de l'arithmétique mixte dans la conception de chemins de données. L'étude porte sur la redéfinition des enchaînements combinatoires et séquentiels entre opérateurs et sur l'utilisation d'arbres d'additions (somme). Cette seconde phase a permis d'identifier des règles d'optimisations génériques liées à l'usage d'opérateurs arithmétiques dans une architecture.

La troisième phase est consacrée à la prise en compte de nouveaux systèmes de représentations dans la la synthèse d'architecture. Nous nous intéressons essentiellement à la phase de traduction comportements — structures physiques. L'objectif est de proposer une méthode de projection équivalente à celle utilisée dans la synthèse bas niveau, incorporant en plus les opérateurs arithmétiques et le savoir-faire lié à leur usage. Pour répondre à ces particularités, la projection ne se fait pas directement vers une bibliothèque de cellules pré-caractérisées, mais vers des générateurs d'architectures. Cette dernière phase a donné lieu à la définition d'une méthodologie de conception de chemins de données basée sur l'utilisation de générateurs de fonctions élémentaires et à la spécification d'un outil d'aide à la conception de chemins de données. Ce dernier permet de définir un chemin de données par une description simplifiée.

#### Mots clefs:

Arithmétique des ordinateurs, systèmes classiques de numération, systèmes redondants de numération, algorithmes et opérateurs arithmétiques, IP core, optimisations arithmétiques, synthèse de chemins de données arithmétiques.

## **Abstract**

This thesis presents the integration of redundant number representations in arithmetic circuit design flow. The work is divided in three parts.

The first part is dedicated to the introduction of the redundant number systems in addition to the classical number systems. For that purpose we have defined a new arithmetic, named *mixed arithmetic*, which takes into account the problems of the simultaneous use of classic and redundant notations. We have also developed a set of new operators which ensure all the possible input / output combinations in redundant and classical notations. The three elementary operations: addition (two operands), sum (more than two operands) and multiplication, have been studied. For each one we have created a generator. The generation parameter list is composed of the size, the sign and the notation of all inputs/outputs, and of the computation algorithm to use.

The aim of the second part is to study the impact of the mixed arithmetic in data path design. The analysis concerns the choice of the notations used between the different operators of an architecture. Combinatorial and sequential chains have been studied. The analysis also applies to the use of the addition tree properties (sum properties). This part allowed us to identify several generic rules of arithmetic optimizations in arithmetic circuit design.

The third part is dedicated to the introduction of the mixed arithmetic in the architecture synthesis. We are essentially interested in the behavioral-to-structural conversion. The goal is to propose a mapping phase taking into account the arithmetic operators and our knowledge in their usage. Therefore, the mapping is not directly based on standard cells but on a generator set. These generators build the operator architectures (standard cells based netlist) depending on the context. For this last part, first we present a arithmetic data path synthesis methodology using basic function generators then we propose the specification of a data path synthesis aid tool. The defined tool input is a simplified data path description.

#### **Keywords:**

Computer arithmetic, classical number systems, redundant number systems, arithmetic operators and algorithms, IP core, arithmetic optimization, arithmetic datapath synthesis.

# Table des matières

| C | Juvei | ture     |                                                               | ,     |

|---|-------|----------|---------------------------------------------------------------|-------|

| * | Ava   | nt-Prop  | 208                                                           | v     |

| * | Rés   | umé      |                                                               | vii   |

| * | Abs   | tract    |                                                               | ix    |

| * | Tab   | le des r | natières                                                      | xi    |

| * | Tab!  | le des f | igures                                                        | xvii  |

| * | List  | e des ta | ableaux                                                       | xxi   |

| * | Glo   | ssaire   |                                                               | xxiii |

| * |       | oductio  |                                                               | 1     |

|   | Con   | texte d  | e recherche                                                   | 1     |

|   | Mot   | ivation  | s et objectifs                                                | 2     |

|   | Con   | tenu dı  | u mémoire                                                     | 3     |

| 1 | Arit  | hmétic   | que et synthèse d'architectures                               | 5     |

|   | 1.1   | Arithi   | métique des ordinateurs                                       | 5     |

|   |       | 1.1.1    | Evolution de l'arithmétique dans les circuits numériques      | 5     |

|   |       | 1.1.2    | Systèmes de représentations                                   | 6     |

|   | 1.2   | Conce    | eption automatisée d'architectures / synthèse d'architectures | 11    |

|   |       | 1.2.1    | Synthèse de système                                           | 11    |

|   |       | 1.2.2    | Synthèse de haut niveau                                       | 12    |

|   |       | 1.2.3    | Synthèse au niveau transfert de registers (RTL)               | 13    |

|   | 1.3   | Proble   | ématique                                                      | 16    |

|   |       | 1.3.1    | Arithmétique minimum                                          | 16    |

|   |       | 1.3.2    | Conception automatisée                                        | 17    |

|   |       | 1.3.3    | Notre problématique                                           | 20    |

| 2 | Arit | hmétiq | que Mixte                                             | 21 |

|---|------|--------|-------------------------------------------------------|----|

|   | 2.1  | Arithr | métique Classique (NR)                                | 21 |

|   |      | 2.1.1  | Représentations                                       | 21 |

|   |      | 2.1.2  | Remarques générales :                                 | 22 |

|   | 2.2  | Arithr | nétique Redondante (R)                                | 22 |

|   |      | 2.2.1  | Représentations                                       | 22 |

|   |      | 2.2.2  | Remarques générales                                   | 24 |

|   | 2.3  | Arithr | nétique Mixte                                         | 25 |

|   |      | 2.3.1  | Compatibilité des données en arithmétique mixte       | 26 |

|   |      | 2.3.2  | Passerelle entre notations mixtes                     | 26 |

|   |      | 2.3.3  | Remarques générales :                                 | 29 |

|   | 2.4  | Concl  | usion                                                 | 30 |

| 3 | Opé  |        | s élémentaires en arithmétique mixte : Architectures  | 31 |

|   | 3.1  | Quelq  | ues remarques préliminaires                           | 31 |

|   |      | 3.1.1  | Choix des opérateurs arithmétiques                    | 31 |

|   |      | 3.1.2  | Problématique des entrées/sorties                     | 32 |

|   |      | 3.1.3  | Remarques sur les architectures                       | 33 |

|   | 3.2  | Addit  | ion entière                                           | 33 |

|   |      | 3.2.1  | Addition élémentaire                                  | 35 |

|   |      | 3.2.2  | Addition Entière non redondante, signée et non signée | 36 |

|   |      | 3.2.3  | Addition Entière mixte, signée et non signée          | 41 |

|   |      | 3.2.4  | Addition Entière redondante, signée et non signée     | 44 |

|   | 3.3  | Somm   | ne                                                    | 48 |

|   |      | 3.3.1  | Algorithme                                            | 48 |

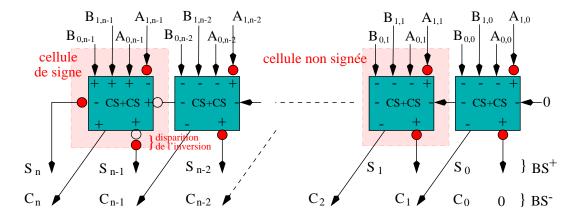

|   |      | 3.3.2  | Sommes signées                                        | 50 |

|   |      | 3.3.3  | Sommes classique, mixte et redondante                 | 51 |

|   |      | 3.3.4  | Remarques et bilan                                    | 52 |

|   | 3.4  | Multip | plication Entière                                     | 53 |

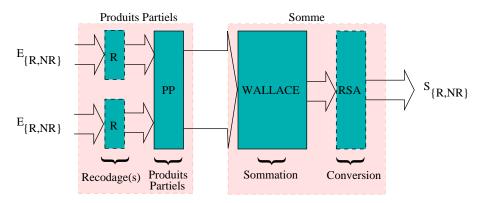

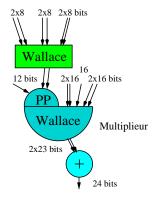

|   |      | 3.4.1  | Multiplication entière non redondante                 | 54 |

|   |      | 3.4.2  | Multiplication entière redondante                     | 56 |

|   |      | 3.4.3  | Multiplication entière mixte                          | 62 |

|   |      | 3.4.4  | Multiplication signée                                 | 67 |

|   | 3.5  | Autre  | s usages des opérateurs mixtes et redondants          | 67 |

|   | 3.6  | Concl  | usion / Bilan                                         | 68 |

| 4 | Opé | érateurs | s élémentaires en arithmétique mixte : Performances             | 69  |

|---|-----|----------|-----------------------------------------------------------------|-----|

|   | 4.1 | Evalua   | ation et comparaison                                            | 69  |

|   |     | 4.1.1    | Méthodologie d'évaluation                                       | 69  |

|   |     | 4.1.2    | Critères d'évaluation                                           | 70  |

|   |     | 4.1.3    | Outils d'évaluations                                            | 70  |

|   |     | 4.1.4    | Comparaison                                                     | 71  |

|   |     | 4.1.5    | Un mot sur la réalisation matérielle des architectures          | 71  |

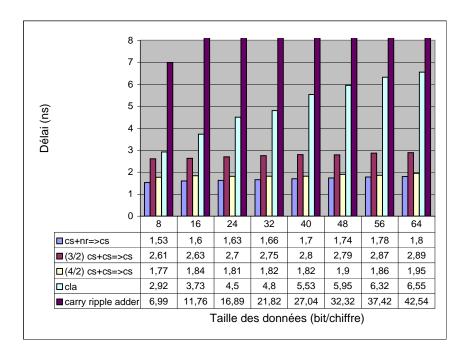

|   | 4.2 | Evalu    | ation des additionneurs                                         | 72  |

|   |     | 4.2.1    | Délai                                                           | 72  |

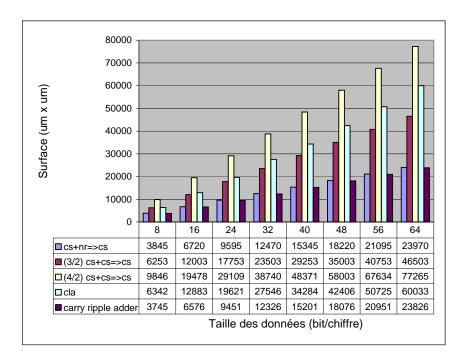

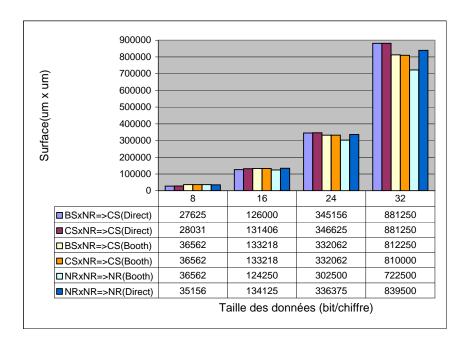

|   |     | 4.2.2    | Surface                                                         | 74  |

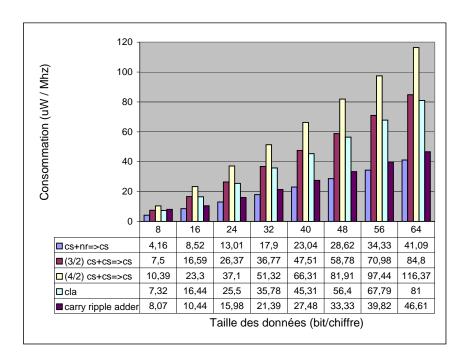

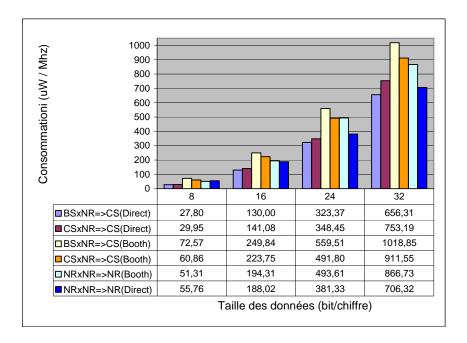

|   |     | 4.2.3    | Consommation                                                    | 75  |

|   |     | 4.2.4    | Synthèse                                                        | 76  |

|   | 4.3 | Evalua   | ation de la somme                                               | 77  |

|   |     | 4.3.1    | Délai                                                           | 77  |

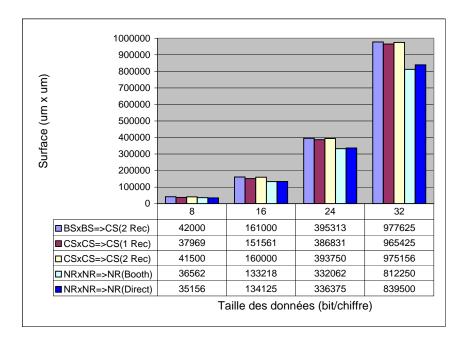

|   |     | 4.3.2    | Surface                                                         | 77  |

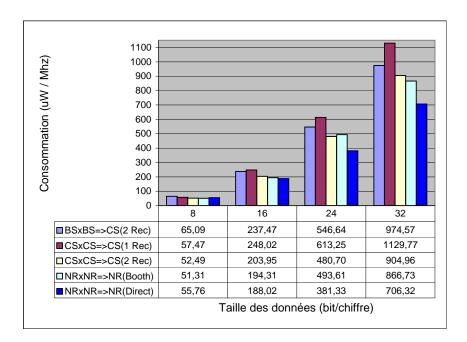

|   |     | 4.3.3    | Consommation                                                    | 78  |

|   |     | 4.3.4    | Synthèse                                                        | 78  |

|   | 4.4 | Evalua   | ation des multiplieurs                                          | 79  |

|   |     | 4.4.1    | Choix de la référence de comparaison                            | 79  |

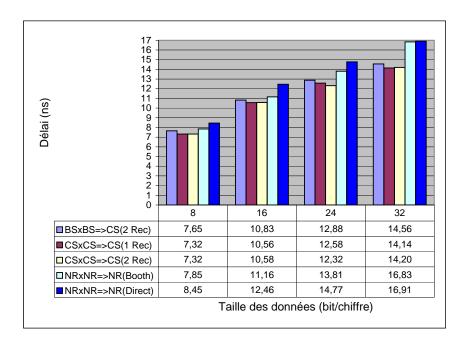

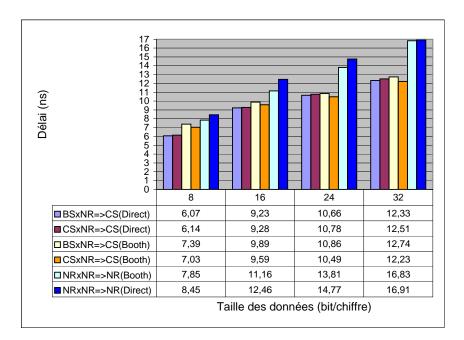

|   |     | 4.4.2    | Délai                                                           | 80  |

|   |     | 4.4.3    | Surface                                                         | 82  |

|   |     | 4.4.4    | Consommation                                                    | 85  |

|   |     | 4.4.5    | Synthèse                                                        | 87  |

|   | 4.5 | Concl    | usion / Bilan                                                   | 88  |

|   |     |          |                                                                 |     |

| 5 |     |          | enchaînements d'opérateurs                                      | 89  |

|   | 5.1 |          | înement dans un circuit combinatoire                            | 89  |

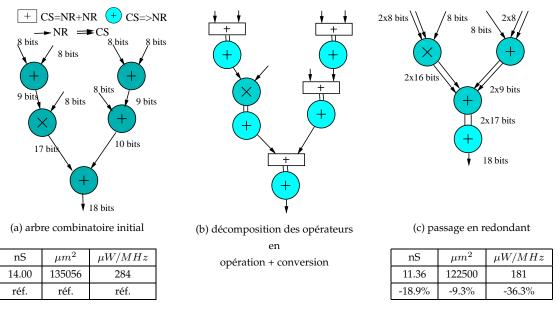

|   |     | 5.1.1    | Passage en tout redondant                                       | 90  |

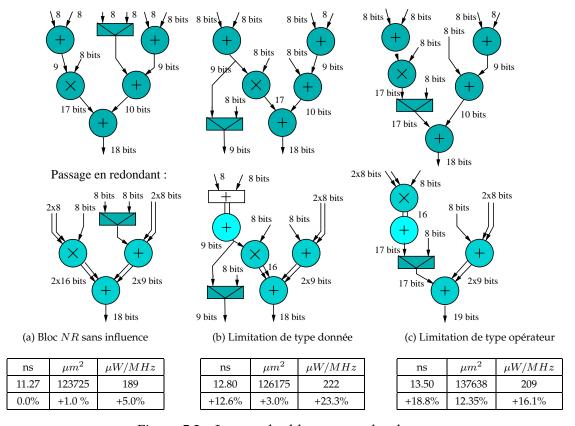

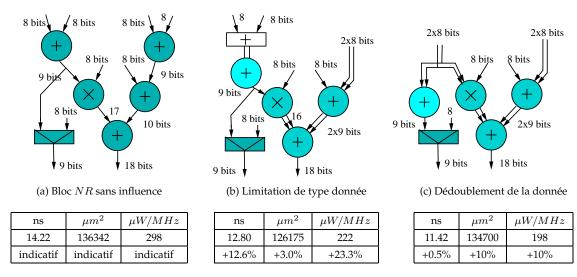

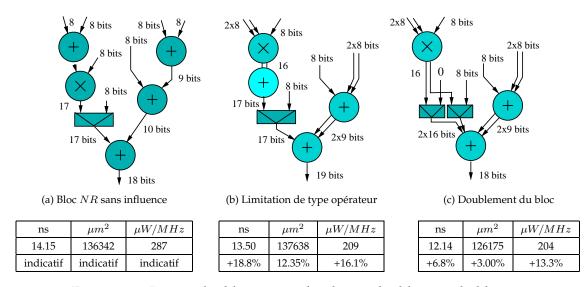

|   |     | 5.1.2    | Impact des blocs n'acceptant pas les notations redondantes      | 91  |

|   |     | 5.1.3    | Intégration de l'aspect temporel des enchaînements d'opérateurs | 94  |

|   |     | 5.1.4    | Enchaînements combinatoires : Synthèse                          | 97  |

|   | 5.2 | Encha    | înement dans un circuit séquentiel                              | 97  |

|   |     | 5.2.1    | Passage d'un point mémorisant                                   |     |

|   |     | 5.2.2    | Analyse temporelle / Aspect temporel                            | 99  |

|   |     | 5.2.3    | Cas particulier du passage d'une chaîne de registres            |     |

|   |     | 5.2.4    | Problèmes inhérents aux rebouclages                             | 102 |

|   |      | 5.2.5   | Enchaînements séquentiels : Synthèse                              | 104 |

|---|------|---------|-------------------------------------------------------------------|-----|

|   | 5.3  | Notat   | ions redondantes partielles                                       | 105 |

|   |      | 5.3.1   | Usage local des notations redondantes                             | 105 |

|   |      | 5.3.2   | Retour partiel en NR                                              | 106 |

|   |      | 5.3.3   | Remarques et conclusions sur les notations redondantes partielles | 110 |

|   | 5.4  | Rema    | rques et Conclusions sur la redéfinition des enchaînements        | 111 |

| 6 | Reg  | roupen  | nent, fusion et glissement d'opérateurs                           | 113 |

|   | 6.1  | Quelq   | ques remarques préliminaires                                      | 114 |

|   | 6.2  | Regro   | oupement d'Opérateurs                                             | 115 |

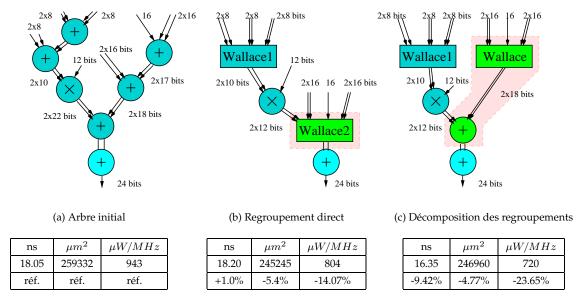

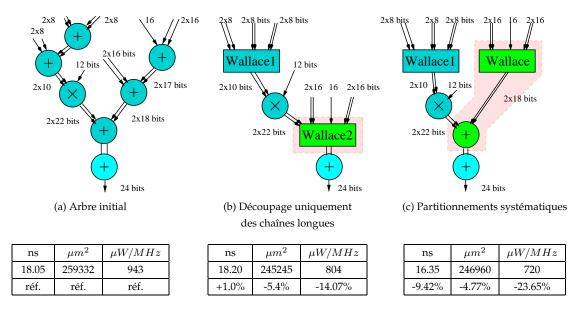

|   |      | 6.2.1   | Remplacement d'un arbre d'additions par un regroupement unique    | 116 |

|   |      | 6.2.2   | Prise en compte de l'aspect temporel dans les de regroupements    | 118 |

|   |      | 6.2.3   | Analyse de temps                                                  | 119 |

|   |      | 6.2.4   | Regroupement: synthèse                                            | 123 |

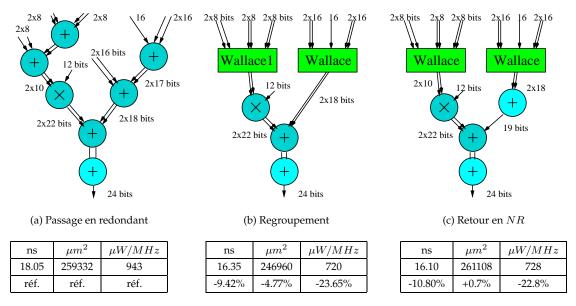

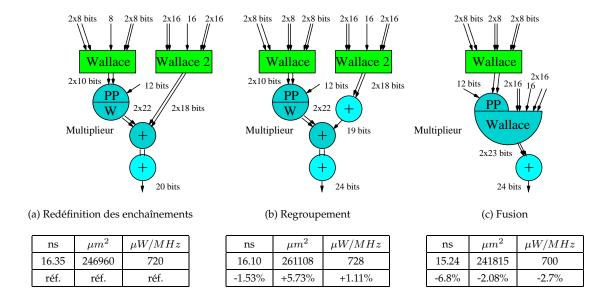

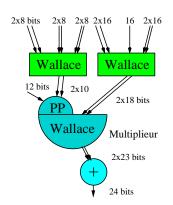

|   | 6.3  | Fusion  | n d'Opérateurs                                                    | 123 |

|   |      | 6.3.1   | Exemple de fusion                                                 | 124 |

|   |      | 6.3.2   | Aspect temporel                                                   | 125 |

|   |      | 6.3.3   | Fusion systématique                                               | 127 |

|   |      | 6.3.4   | Fusion: synthèse                                                  | 128 |

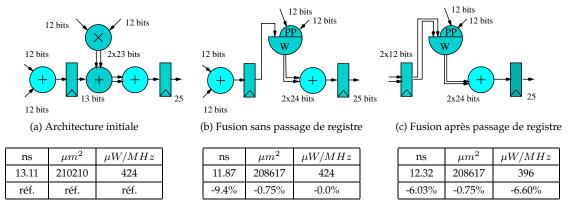

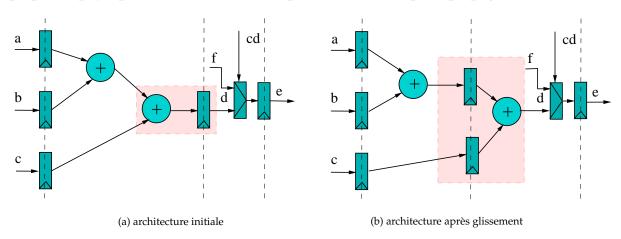

|   | 6.4  | Glisse  | ement d'opérateurs                                                | 129 |

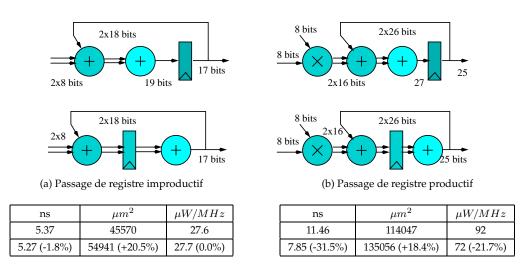

|   |      | 6.4.1   | Glissement entier de bloc                                         | 130 |

|   |      | 6.4.2   | Glissement partiel de bloc ou absorption de registre              | 132 |

|   |      | 6.4.3   | Glissement et blocs neutres                                       | 132 |

|   | 6.5  | Concl   | usion                                                             | 133 |

| 7 | Vers | s un ou | til d'aide à la conception de chemin de données arithmétique      | 135 |

|   | 7.1  | Rema    | rques préliminaires et objectifs détaillés                        | 136 |

|   |      | 7.1.1   | Entrées/sorties                                                   | 136 |

|   |      | 7.1.2   | Encapsulation de notre savoir-faire arithmétique                  | 137 |

|   |      | 7.1.3   | Association et réutilisation de travaux antérieurs / Portabilité  | 139 |

|   |      | 7.1.4   | Traitements et méthodologie générale d'optimisation               | 140 |

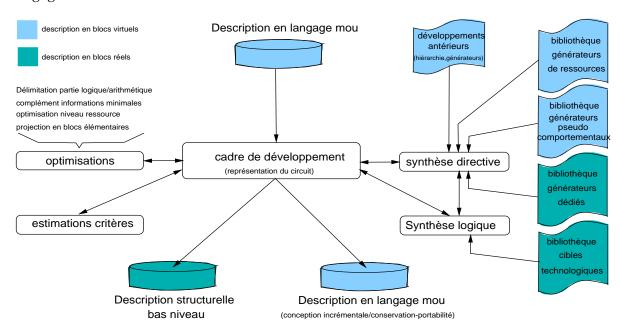

|   |      | 7.1.5   | Cadre de développement                                            | 142 |

|   | 7.2  | Métho   | odologie de conception de générateurs et projection               |     |

|   |      | 7.2.1   | Génération et projection                                          |     |

|   |      | 7.2.2   | Génération et cadre de développement                              |     |

|   |      | 7.2.3   | Synthèse                                                          |     |

|            | 7.3  | Traitements et Optimisations                                                    | 150 |

|------------|------|---------------------------------------------------------------------------------|-----|

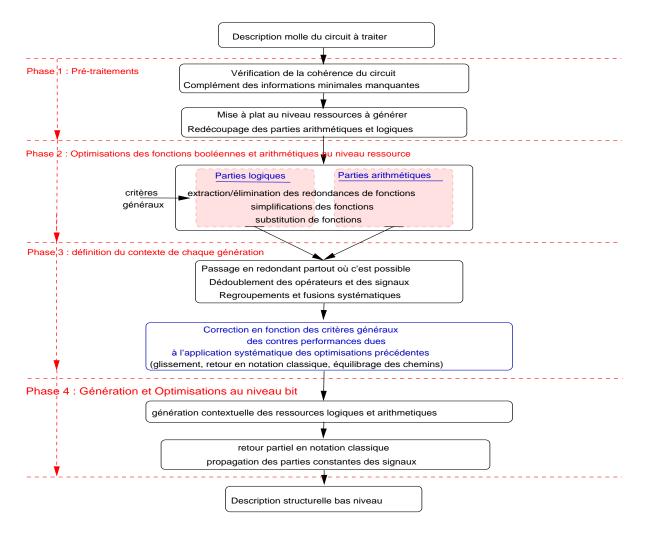

|            |      | 7.3.1 Méthodologie générale d'optimisation, traitements associés                | 150 |

|            |      | 7.3.2 Application des optimisations arithmétiques                               | 153 |

|            |      | 7.3.3 Optimisation selon les critères généraux                                  | 154 |

|            |      | 7.3.4 Évaluation des critères généraux                                          | 155 |

|            |      | 7.3.5 Synthèse                                                                  | 156 |

|            | 7.4  | Cadre de développement                                                          | 157 |

|            |      | 7.4.1 Vision générale du cadre de développement                                 | 157 |

|            |      | 7.4.2 Impact de l'arithmétique mixte sur les éléments de base de la description | 158 |

|            |      | 7.4.3 Synthèse                                                                  | 160 |

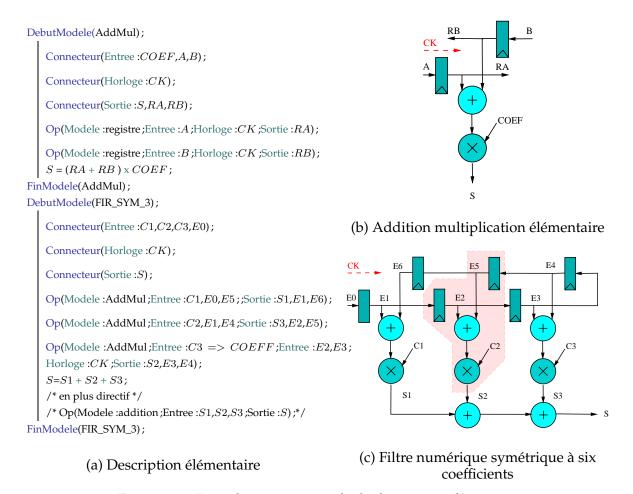

|            | 7.5  | Langage de description mou                                                      | 160 |

|            |      | 7.5.1 Contraintes                                                               | 160 |

|            |      | 7.5.2 Proto-langage                                                             | 161 |

|            |      | 7.5.3 Langage et génération                                                     | 163 |

|            |      | 7.5.4 Synthèse                                                                  | 164 |

|            | 7.6  | Vision globale de l'outil de conception                                         | 165 |

|            | 7.7  | Conclusion                                                                      | 166 |

| k          | Con  | clusions et perspectives                                                        | 169 |

|            | Con  | clusions                                                                        | 169 |

|            | Pers | pective                                                                         | 170 |

| k          | Bibl | iographie                                                                       | 173 |

| k          | List | e des publications                                                              | 179 |

| <b>4</b> 1 | nnex | es 1                                                                            | 181 |

|            |      |                                                                                 |     |

| 4          |      | 1                                                                               | 183 |

|            |      | Introduction                                                                    |     |

|            | A.2  | Algorithme de Booth                                                             |     |

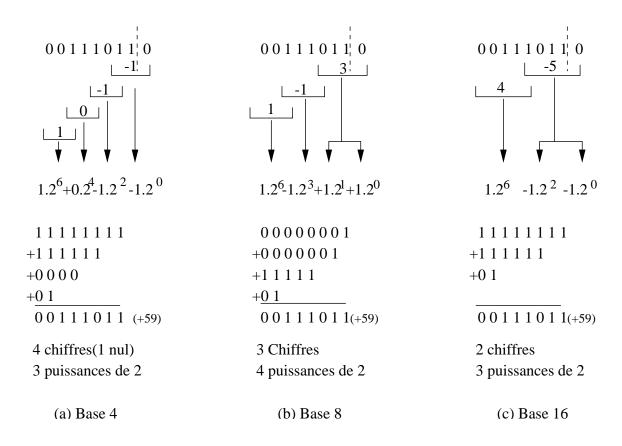

|            |      | A.2.1 Algorithme de Booth en base 2 exposant M, M constant                      |     |

|            | ۸. ۵ | A.2.2 Nombre variable de bases                                                  |     |

|            |      | Multiplieurs mixtes par une constante                                           |     |

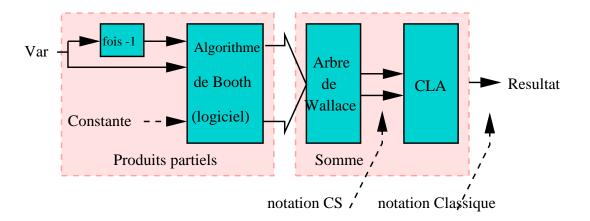

|            | A.4  | Architecture                                                                    |     |

|            |      | A.4.1 Architecture globale                                                      |     |

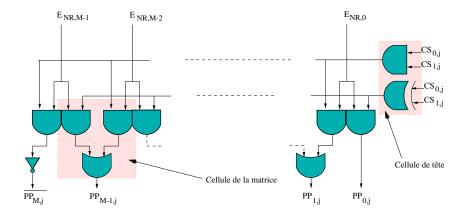

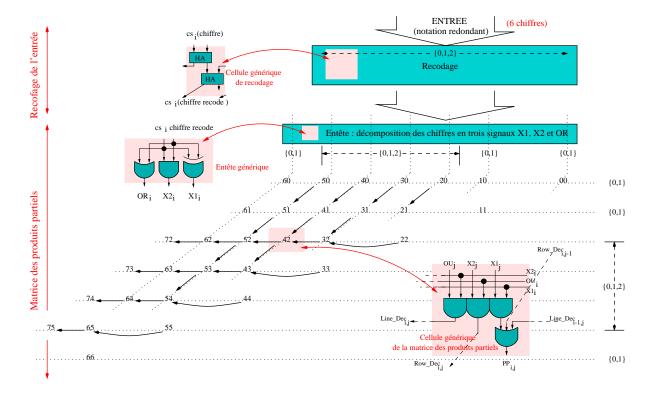

|            |      | A.4.2 Matrice des produits partiels                                             | 189 |

## Table des matières

|   |      | A.4.3    | Somme                                             | 189 |

|---|------|----------|---------------------------------------------------|-----|

|   | A.5  | Résult   | rats                                              | 189 |

|   |      | A.5.1    | Algorithme                                        | 189 |

|   |      | A.5.2    | Réalisations matérielles                          | 191 |

|   | A.6  | Concl    | usion                                             | 194 |

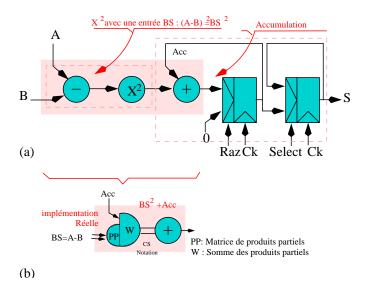

| В | Carr | é et cal | cul de distance                                   | 195 |

|   | B.1  | Introd   | uction                                            | 195 |

|   | B.2  | Archit   | ectures associées au Carré                        | 195 |

|   |      | B.2.1    | Opérateur Carré : Principe                        | 195 |

|   |      | B.2.2    | Opérateur carré en notation classique             | 196 |

|   |      | B.2.3    | Carré en notation redondante                      | 197 |

|   | B.3  | Unité    | de calcul de distances (DCU)                      | 198 |

|   | B.4  | Résult   | ats et comparaison                                | 199 |

|   |      | B.4.1    | Performance des opérateurs de carré               | 199 |

|   |      | B.4.2    | Performance des opérateurs de calcul de distances | 200 |

|   | В5   | Concl    | usion                                             | 202 |

# Table des figures

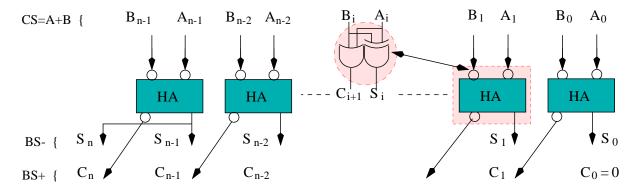

| 2.1  | Conversion $CS \to BS$                                                                    | 28 |

|------|-------------------------------------------------------------------------------------------|----|

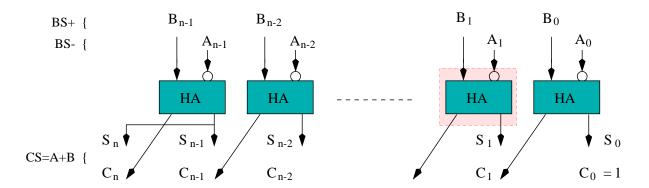

| 2.2  | Conversion $BS \to CS$                                                                    | 29 |

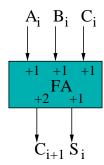

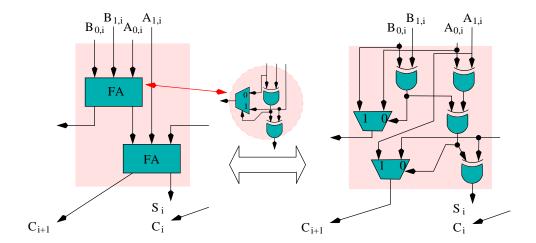

| 3.1  | Additionneur élémentaire                                                                  | 35 |

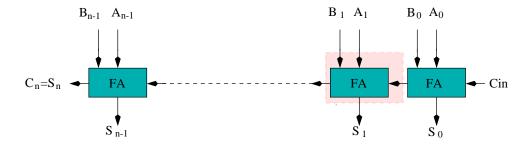

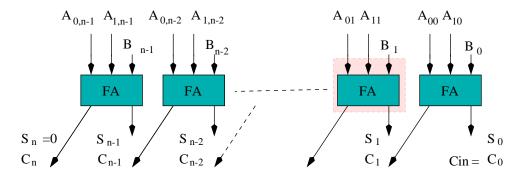

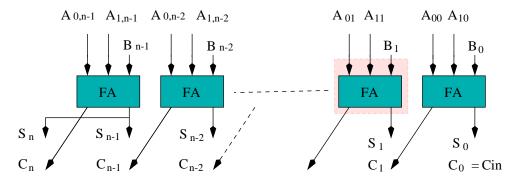

| 3.2  | Additionneur séquentiel non signé                                                         | 37 |

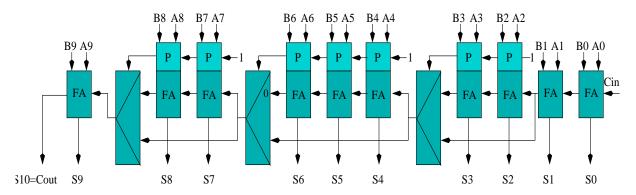

| 3.3  | Additionneur 10 bits à saut de retenue en non signé                                       | 38 |

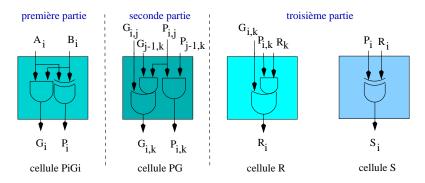

| 3.4  | Addition à retenue anticipée : Cellules élémentaires                                      | 39 |

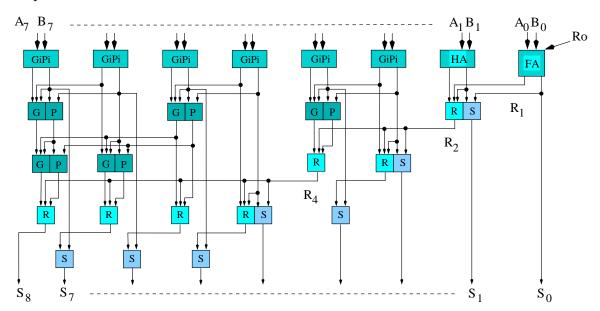

| 3.5  | Additionneur 8 bits à retenue anticipée                                                   | 39 |

| 3.6  | Additionneur: gestion de signe                                                            | 40 |

| 3.7  | Addition mixte non signée                                                                 | 42 |

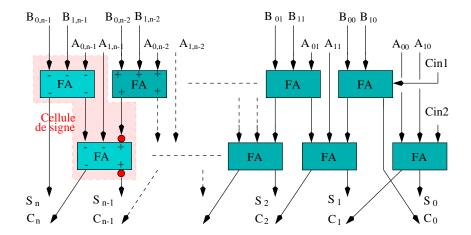

| 3.8  | Addition mixte signée                                                                     | 42 |

| 3.9  | Cellule élémentaire de soustraction                                                       | 43 |

| 3.10 | Addition redondante signée de type 3/2                                                    | 44 |

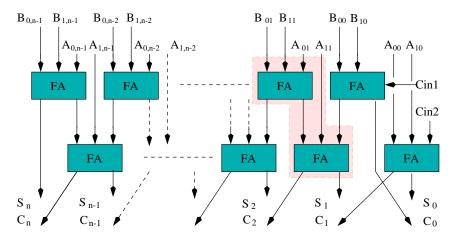

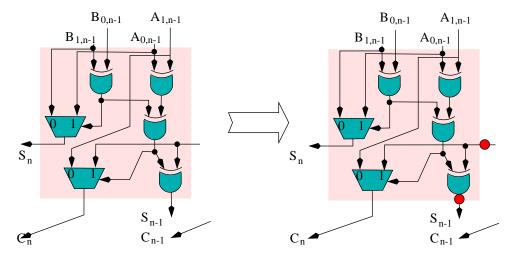

| 3.11 | Addition redondante non signée de type 4/2                                                | 45 |

| 3.12 | Addition redondante signée de type 3/2 (Full-Adder)                                       | 46 |

| 3.13 | Addition redondante signée 4/2                                                            | 46 |

| 3.14 | Soustraction redondante                                                                   | 48 |

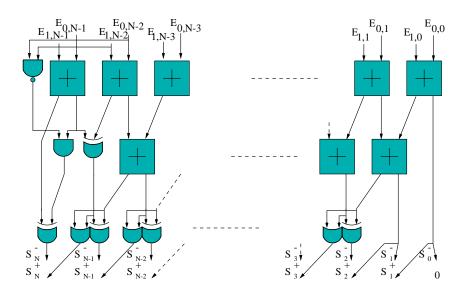

| 3.15 | Somme à partir de la matrice de produits partiels d'un multiplieur $7x7 \ldots \ldots$    | 50 |

| 3.16 | Multiplieur générique                                                                     | 53 |

| 3.17 | Multiplieur $Direct$ : produits partiels $A_{NR} \cdot B_{NR,i \neq N-1}$ signés          | 55 |

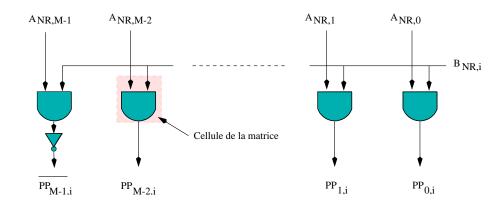

| 3.18 | Multiplieur de $Booth$ : produits partiels $A_{NR} \cdot B_{NR,i}$ signés                 | 56 |

| 3.19 | Multiplication redondante : Architecture associée aux produits partiels                   | 58 |

| 3.20 | Multiplication redondante : recodage signé en deux étages                                 | 59 |

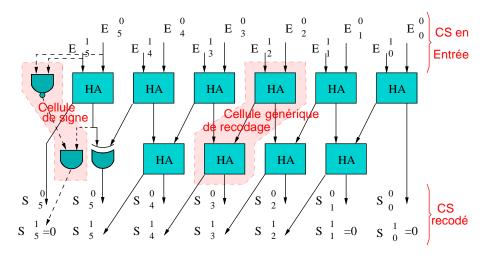

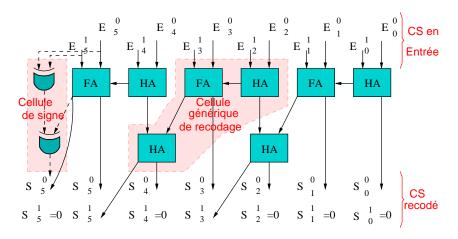

| 3.21 | Modification de l'étage de recodage : exemple avec un $CS$ sur 6 chiffres $\ldots \ldots$ | 60 |

| 3.22 | Multiplication redondante : ajustement de la dynamique                                    | 61 |

| 3.23 | Multiplication redondante : recodage d'une entrée BS                                      | 61 |

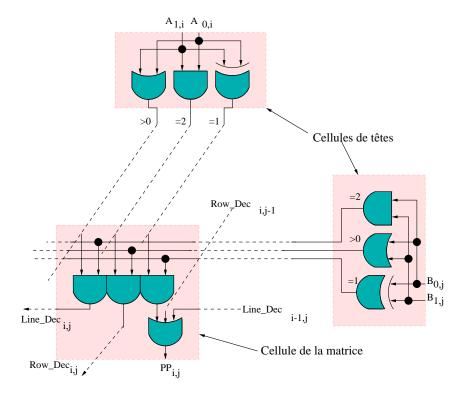

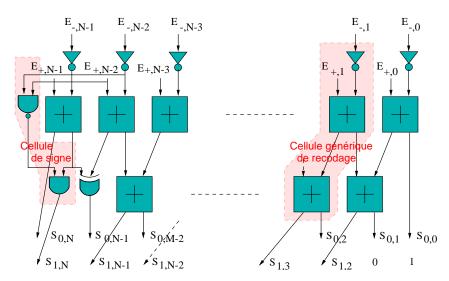

| 3.24 | Multiplication mixte $Directe$ : produits partiels $CS_j \cdot E_{NR}$ signés             | 63 |

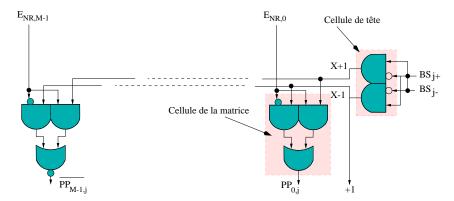

| 3.25 | Multiplication mixte $Directe$ : produits partiels $BS_j \cdot E_{NR}$ signés             | 63 |

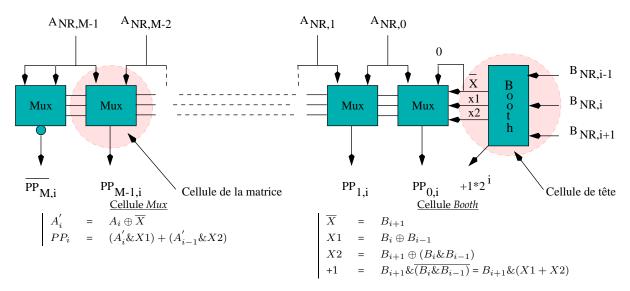

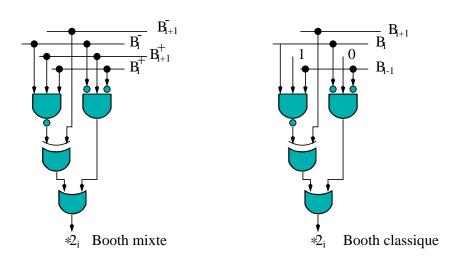

| 3.26 | Multiplication de <i>Booth</i> mixte : étage de recodage supplémentaire                   | 65 |

| 3.27 | Multiplieur de <i>Booth</i> mixte : correspondance entre cellule <i>Booth</i>             | 66 |

| 4.1  | Additionneurs : comparaison en délai                                                      | 73 |

| 4.2  | Additionneurs: comparaison en surface                                                           |

|------|-------------------------------------------------------------------------------------------------|

| 4.3  | Additionneurs: comparaison en consommation                                                      |

| 4.4  | Multiplieurs mixtes : comparaison en délai                                                      |

| 4.5  | Multiplieurs redondants : comparaison en délai                                                  |

| 4.6  | Multiplieurs mixtes: comparaison en surface                                                     |

| 4.7  | Multiplieurs redondants : comparaison en surface                                                |

| 4.8  | Multiplieurs mixtes: comparaison en consommation                                                |

| 4.9  | Multiplieurs redondants : comparaison en consommation                                           |

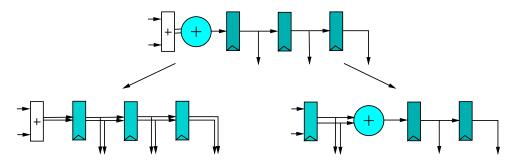

| 5.1  | Passage en tout redondant                                                                       |

| 5.2  | Impact des blocs non redondants                                                                 |

| 5.3  | Impact des blocs non redondants : double représentation                                         |

| 5.4  | Impact des blocs non redondants : doublement du bloc $NR$                                       |

| 5.5  | Aspect temporel des enchaînements                                                               |

| 5.6  | Analyse de temps                                                                                |

| 5.7  | Redéfinition des enchaînements des registres isolés                                             |

| 5.8  | Enchaînement séquentiel : analyse temporelle                                                    |

| 5.9  | traitement d'une chaîne de registres                                                            |

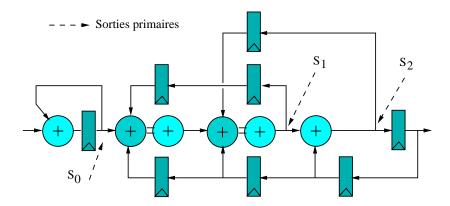

| 5.10 | Boucles : illustration des sorties primaires                                                    |

| 5.11 | Boucles : Passage en redondant                                                                  |

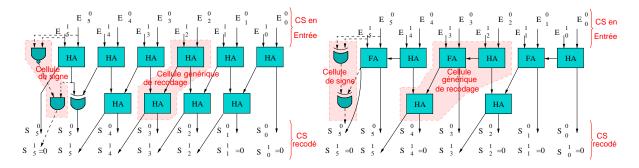

|      | Multiplication redondante : architectures des recodages $R \to R$ 105                           |

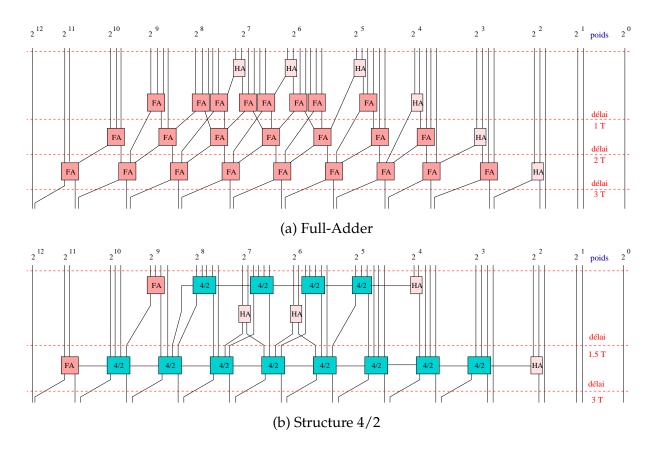

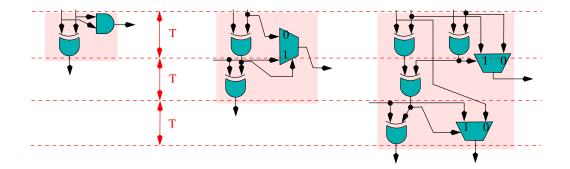

| 5.13 | Délai respectif des cellules $HA$ , $FA$ et $4/2$                                               |

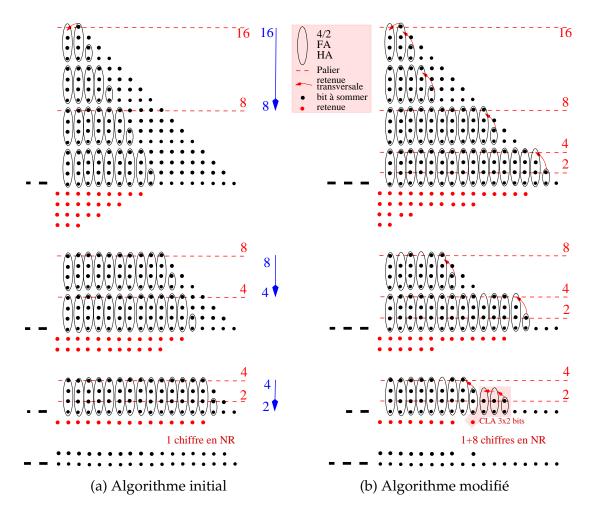

| 5.14 | Retour partiel en $NR$ : réduction des produits partiels d'un multiplieur $16x16$ $109$         |

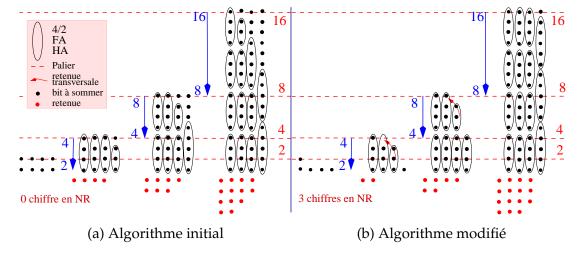

| 5.15 | Retour partiel en $NR$ : facteur de forme rectangulaire                                         |

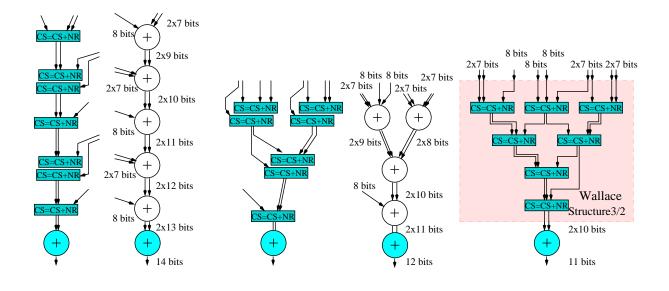

| 6.1  | Exemple de regroupement                                                                         |

| 6.2  | Disponibilité des Entrées                                                                       |

| 6.3  | Regroupements : Application de l'analyse des temps                                              |

| 6.4  | Retour en notation non redondante                                                               |

| 6.5  | Exemple de fusion                                                                               |

| 6.6  | Fusion: analyse de temps                                                                        |

| 6.7  | Fusion Systématique                                                                             |

| 6.8  | Glissements entiers $a \to b \ (E \to S)$ et $b \to a \ (S \to E)$ : impact sur les données 130 |

| 6.9  | Glissement entier : signal de commande                                                          |

| 6.10 | Glissement des blocs neutres                                                                    |

| 7.1  | Principe de génération et de projection                                                         |

## Table des figures

| 7.2 | Génération intermédiaire                                                                                                                                                    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.3 | Méthodologie d'optimisation                                                                                                                                                 |

| 7.4 | Proto-langage: exemple de description d'un circuit                                                                                                                          |

| 7.5 | Principe de l'outil d'aide à la conception                                                                                                                                  |

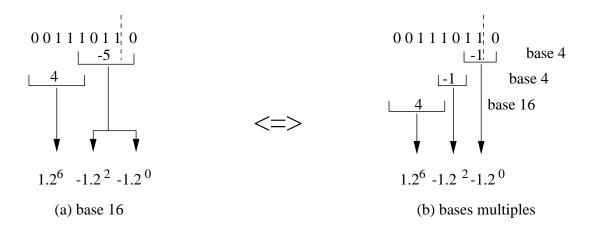

| A.1 | Décomposition en puissance de deux de $59_{(00111011)}$                                                                                                                     |

| A.2 | Vers l'usage simultané de plusieurs bases                                                                                                                                   |

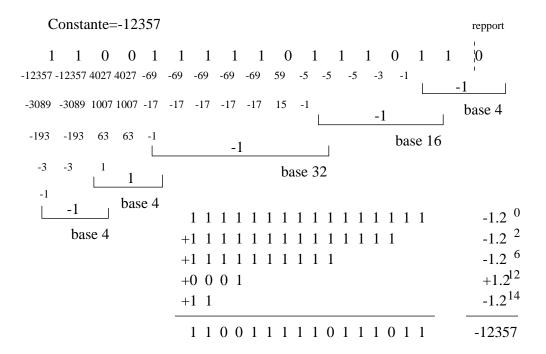

| A.3 | Algorithme de Booth en base variable                                                                                                                                        |

| A.4 | Exemple de décomposition en base multiple                                                                                                                                   |

| A.5 | Multiplication par une constante : architecture globale                                                                                                                     |

| A.6 | Comparaison avec un multiplieur $variable \cdot variable \dots \dots$ |

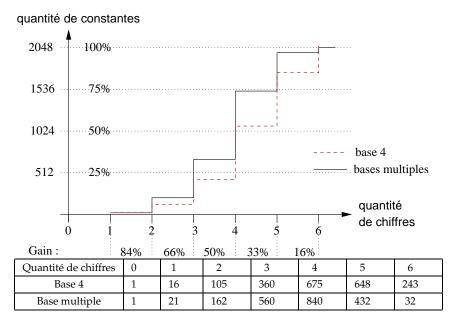

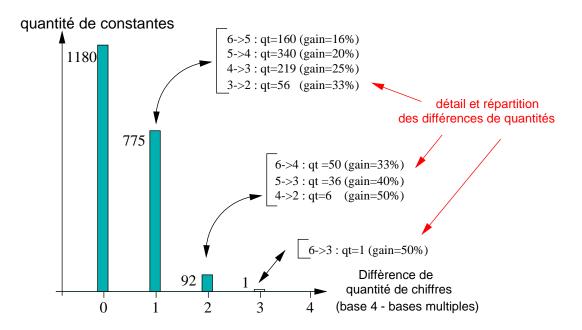

| A.7 | Différence de quantité de chiffres entre les encodages en base 4 et en bases mul-                                                                                           |

|     | tiples                                                                                                                                                                      |

| B.1 | Réduction de la matrice de produits partiels                                                                                                                                |

| B.2 | Carré redondant : détail du calcul des produits partiels pour une entrée sur 6                                                                                              |

|     | chiffres                                                                                                                                                                    |

| B.3 | Unité de calcul de distance ( <i>DCU</i> )                                                                                                                                  |

# Liste des tableaux

| 2.1 | Intervalle de définition des notations mixtes                         | 26  |

|-----|-----------------------------------------------------------------------|-----|

| 3.1 | Table de vérité des signaux de propagation et de génération           | 37  |

| 3.2 | Algorithmes de Booth                                                  | 55  |

| 3.3 | Multiplication de <i>Booth</i> mixte : cellule <i>Booth</i>           | 66  |

| A.1 | Exemples d'applications des encodages en base 4 et en bases multiples | 193 |

| B.1 | Performances du carré et de l'unité de calcul de distance             | 201 |

## Glossaire

**ALU** — Arithmetic and Logic Unit — Unité Arithmétique et Logique **ASIC** — Application-Specific Integrated Circuit — Circuit intégré spécifique conçu pour réaliser de façon optimale une fonction précise dans un système. **ASIP**  — Application-Specific Instruction set Processor — Coeur de processeur spécialisé et optimisé, offrant un compromis entre efficacité et flexibilité BS Notation Borrow-Save C2 Notation en Complément à 2 CAO Conception Assitée par Ordinateur **CLB** — Configuable Logic Block — Bloc logique programmable dans les circuits *FPGA* co-design Conception Matérielle/Logicielle: Méthodologie de conception visant la réduction de l'écart entre l'implantation d'une fonction sur un ASIC ou en logiciel. Elle permet la conception simultanée de systèmes hétérogène impliquant des ASICs et des processeurs de type général. CS Notation Carry-Save **DCT** — Discret cosine Transform — Transformée cosinus discrète DSP — Digital Signal Processor — Processeur spécialisé pour les applications du traitement du signal et de l'image. FA — Full-Adder — Cellule élémentaire additionneur **FFT** — Fast Fourrier Transform — Transformée discrète de Fourrier rapide FIR-IIR — FIR/IIR — Finite Impulse Response / Infinite Impluse Response — Filtres numériques à réponse impulsionnelle finie ou infinie. **FPGA** — Field Programmable Gate Array — Circuit spécifique dont la fonctionnalité est programmée par l'utilisateur. Full-Custom Technique de réalisation matérielle dédiée d'un bloc ou d'un circuit; en VLSI la description est faite au niveau transistor. **GSM** — Global System for Mobile Communication — Standard de téléphonie mobile utilisé en Europe et dans une grande partie du monde. H26X Ensemble de normes d'encodage et de décodage de vidéos bas débits, mis en place par le groupe *UIT-T* : http ://www.itu.int/

HA — Half-Adder — Cellule élémentaire demi-additionneur

HDTV — High Definition TV — Télévision Haute définition, norme de diffusion de la télévision par cable et réseau hertzion, basée sur la norme MPEC 2

télévision par cable et réseau hertzien, basée sur la norme MPEG-2

IP — Intellectual Property — Terme désignant une fonction réutilisable, pré-construite, et pouvant exister sous différentes formes (modèle HDL, modèle physique, etc.).

LSB — Lower Significant Bit — Bit/chiffre d'un nombre de poids le moins significatif

MAC — Multiplication-ACcumulation — instruction principale des processeurs de traitement du signal et de l'image (DSP)

tememt du signal et de l'image (DSP)

MPEG — Motion Picture Expert Group — Ensemble de normes d'encodage et de décodage de vidéos haut débits, mis en place par le groupe *ISO-MPEG* :

http://www.mpeg.org/

MSB — Most Significant Bit — Bit/chiffre d'un nombre de poids le plus significatif

NR Notations Non-Redondantes (C2, NSP)

NSP Notation Numération Simple de Position

RAM — Random Access Memory — Mémoire dynamique à accès aléatoire.

RNS — Residu Number System — Notation par résidus.

RTL — Register Transfert Level —

R Notations Redondantes

UMTS — Universal Mobile Telecommunications System — Standard de systèmes de communication mobile pour les téléphones portables de troisième génération, mis en place par the International Telecommunications Union's RIMT-2000G:

http://www.umts-forum.org/.

VERILOG Langage de description de circuits intégrés. Note : VHDL International et Open Verilog International sont actuellement en train de s'assembler dans une nouvelle organisation (ACCELLERA) : http://www.accellera.org.

VHDL — VHSIC (Very High Speed Integrate Circuit) Design Langage — Langage de description de circuits intégrés. Note: VHDL International et Open Verilog International sont actuellement en train de s'assembler dans une nouvelle organisation (ACCELLERA): http://www.accellera.org.

VLSI — Very Large Scale Integration —

## Introduction

#### Contexte de recherche

L'essor important des nouvelles technologies associées à la communication, aux médias, à l'imagerie médicale et à bien d'autres domaines, sont à l'origine de l'émergence de nombreuses applications et de standards liés aux traitements du signal et de l'image : téléphonie (GSM, UMTS), vidéo (H26X, MPEG, HDTV), pour ne citer qu'eux. Un des dénominateurs communs à ces diverses applications est la nécessité de disposer des circuits pouvant effectuer simultanément une énorme quantité de calculs.

Plusieurs approches et types d'architectures cibles ont été développées pour réaliser de tels circuits : principalement les microprocesseurs spécialisés (DSP) où l'application est essentiellement obtenue par programmation logicielle, les coprocesseurs ou circuits spécialisés (ASIC, ASIP) où la réalisation est essentiellement matérielle, les FPGA où l'approche est matérielle mais où la réalisation est reprogrammable par logiciel, et plus récemment des circuits mixtes où l'application est répartie entre logiciel et matériel (co-design). Dans ce dernier cas, les architectures s'articulent autour de bus auxquels sont rattachés plusieurs ressources comme des coprocesseurs, de la mémoire et un ou plusieurs processeurs.

Quels que soient le type d'architecture cible et l'approche choisie, le développement de noyaux de calculs est nécessaire. L'évolution de leur complexité suit celle des applications visées. Aussi, le nombre et la diversité des opérateurs arithmétiques implantés ont augmenté. Les enchaînements d'opérateurs ont fait leur apparition. Cette dernière évolution a ouvert la voie à l'utilisation de systèmes de représentation des nombres comme les systèmes de notations redondantes ou les systèmes de notations par résidus (RNS).

Parallèlement à l'évolution de l'arithmétique dans la micro-électronique, la complexité croissante des applications visées et la durée de vie très courte des produits développés (téléphonie, par exemple) impliquent le besoin de méthodes et d'outils d'aide à la conception. La combinaison de ces deux contraintes s'est traduite par un désengagement des techniques de conception *bas niveau* en faveur de l'automatisation du flot de conception d'architecture.

Schématiquement cette automatisation prend la forme d'outils d'aide à la conception décomposables en trois étapes interdépendantes. Les deux premières opèrent respectivement au niveau de la spécification du système et de l'architecture et résolvent des problèmes comme la répartition logicielle/matérielle ou l'allocation et l'utilisation de ressources. Les solutions mises en

œuvre sont entre autres basées sur des modèles de transactions de données et des modèles comportementaux de blocs élémentaires comme les opérateurs arithmétiques. La troisième étape effectue la traduction des modèles de comportement en modèles physiques. Plusieurs techniques sont utilisables comme la *synthèse logique* ou l'exploitation de générateurs encapsulant un *savoir-faire* (*Intellectual-Property/IP*).

Outre les problèmes de rapidité de prototypage, la raison d'être des évolutions de l'arithmétique et des méthodes de conception, est l'amélioration des performances des circuits réalisés. Historiquement la qualité des circuits s'est mesurée en premier aux résultats en surface, car la taille des circuits était la contrainte majeure. Comme la capacité d'intégration a fortement augmenté cette contrainte est passée au second plan derrière le temps de propagation. Plus récemment la densité d'intégration des circuits et l'ouverture des semi-conducteurs aux applications embarquées ont introduit un nouveau critère essentiel qui est la consommation d'énergie.

## Motivations et objectifs

La principale motivation de ce mémoire est d'introduire les nouveaux systèmes de représentations des nombres, plus précisément les systèmes de notations redondantes, dans le flot de conception de cœurs de calculs. Cette prise en compte nécessite plusieurs étapes.

La première est consacrée à l'introduction des systèmes de notations redondantes aux côtés des systèmes de notations classiques. À cet effet nous définirons une nouvelle arithmétique que nous qualifierons de *mixte* : redondante/classique. Cette arithmétique doit répondre aux problèmes liés à l'usage simultané des notations classiques et redondantes. Cela implique l'étude et le développement d'opérateurs tenant compte de toutes les notations et de toutes les combinaisons de notations sur leurs entrées/sorties.

La deuxième étape a pour objectif de déterminer quel est l'impact de l'arithmétique mixte sur la conception de chemins de données. Elle a aussi pour vocation la recherche de règles d'optimisations générales, automatisables, liées à l'usage d'opérateurs arithmétiques dans une architecture.

La troisième étape est consacrée à la prise en compte de nouveaux systèmes de représentations dans les outils d'aide à la conception. Nous nous intéressons essentiellement à la phase de traduction *comportements vers structures physiques*. Plus précisément, nous visons la spécification d'un outil d'aide à la conception de chemin de données prenant en compte les contraintes introduites par l'usage de plusieurs systèmes de notations des nombres et les contraintes liées à l'emploi d'opérateurs arithmétiques.

#### L'objectif est double :

- 1. Permettre de définir un chemin de données par une description simplifiée. C'est à dire principalement en s'affranchissant des problèmes de dynamique et de représentation des données, et en considérant les opérateurs élémentaires arithmétiques et autres : fonctions booléennes, fonctions de transfert de données, etc., comme de simples mnémoniques.

- 2. Proposer une méthode de projection (*mapping*) équivalente à celle utilisée dans la synthèse logique, mais incorporant en plus les opérateurs arithmétiques et le savoir-faire lié à leur usage. La particularité de ces opérateurs vient de la dimension vectorielle de leurs entrées/sorties, de la représentation arithmétique des données, et de la diversité des performances de leurs possibles architectures. Pour répondre à ces particularités, la projection ne se fait pas directement vers une bibliothèque de cellules pré-caractérisées, mais vers des générateurs d'architectures.

Le savoir-faire ou plutôt les optimisations sous-entendues dans les deux dernières étapes, peuvent s'envisager de plusieurs façons. Dans notre cas, il s'agit de mettre en place des mécanismes permettant l'amélioration de la traduction VLSI d'une architecture liée à un algorithme. Il n'est pas question de retravailler les équations arithmétiques ou de transformer l'architecture développée. En clair, nous allons chercher à tirer parti des qualités de l'arithmétique mixte et des opérateurs qui lui sont rattachés et s'interdire de modifier l'architecture initiale dans son fonctionnement. Ce dernier point implique que l'ajout de matériel et les techniques comme le retiming [Leis83] ou l'insertion de pipeline sont exclus des optimisations. Le comportement de l'architecture optimisée doit être fidèle à l'architecture initiale.

#### Contenu du mémoire

L'ensemble des travaux présentés dans ce mémoire traite de la réalisation matérielle d'applications fortement calculatoires. Ils sont découpés en quatre parties.

Classiquement la première partie est consacrée à la définition des problèmes considérés. Le chapitre 1 *Arithmétique et synthèse d'architectures*, s'y référant, se décompose en deux étapes. La première correspond à un exposé général sur l'arithmétique utilisée en micro-électronique et sur la synthèse d'architecture. La seconde est dédiée plus précisément à la définition de la problématique.

La seconde partie est destinée à la composition d'une arithmétique mixte regroupant les systèmes de notations classiques et redondants. Cette partie est sous divisée en trois chapitres. Le premier (chapitre 2 *Arithmétique Mixte*) est consacré à l'introduction de l'arithmétique redon-

dante auprès de l'arithmétique entière classique et à une réflexion sur leur usage conjoint. Le second (chapitre 3 Opérateurs élémentaires en arithmétique mixte : Architectures) présente les diverses architectures associées aux opérations fondamentales que sont l'addition, la somme et la multiplication. Le troisième (chapitre 4 Opérateurs élémentaires en arithmétique mixte : Performances) est dédié à l'étude des performances intrinsèques des nouveaux opérateurs développés selon les trois critères que sont la puissance consommée, le temps de propagation et la surface. L'objectif est double : à la fois positionner les opérateurs mixtes et redondants par rapport aux opérateurs classiques mais aussi démontrer l'intérêt de l'usage des notations redondantes. La troisième partie a pour objectif l'étude de l'impact de l'arithmétique mixte, dans divers contextes d'utilisations. Elle a aussi pour vocation la recherche de règles d'optimisations automatisables liées à l'usage d'opérateurs arithmétiques dans une architecture. Elle est articulée autour de deux chapitres. Le premier (chapitre 5 Étude des enchaînements d'opérateurs) traite de l'impact des opérateurs mixtes et redondants précédemment développés (addition, somme et multiplication), dans des architectures données. Nous parlerons de problèmes d'enchaînements d'opérateurs. Le second (chapitre 6 Regroupement, fusion et glissement d'opérateurs) est plus centré sur l'utilisation de la somme (addition de plus de deux opérandes) et des registres. Dans ce second cas les optimisations sont plus liées à l'arithmétique en générale et aux chemins

La dernière partie de ces travaux est consacrée à la définition d'un outil d'aide à la conception de chemin de données incluant des traitements arithmétiques. L'idée directrice est d'encapsuler dans un outil, notre *savoir-faire* lié à l'utilisation conjointe de plusieurs systèmes de représentations des nombres et à la réalisation d'opérateurs arithmétiques. L'objectif est de permettre de réutiliser à volonté notre expertise. Plus précisément, les propos développés portent sur la phase de traduction *description de haut niveau*  $\rightarrow$  *description bas niveau* d'un chemin de données. L'objectif est de tendre vers une méthode de projection équivalente à celle utilisée dans la synthèse logique, automatisant le passage d'une description structurelle simplifiée d'un bloc à une description structurelle précise du même bloc. Cette partie est traitée dans le chapitre 7 *Vers un outil d'aide à la conception de chemin de données arithmétique*.

de données en particulier.

## Chapitre

# Arithmétique et synthèse d'architectures

Cette thèse ayant pour but de généraliser l'usage simultané de plusieurs systèmes de représentations des nombres dans la conception automatisée de circuits numériques, nous commencerons par présenter l'arithmétique utilisée et la conception automatisée d'architectures. Ces présentations dépassant le cadre de cette thèse, elles resteront générales. Les détails techniques nous intéressant plus particulièrement seront vus dans les chapitres suivants. Dans un deuxième temps, nous présenterons notre problématique.

## 1.1 Arithmétique des ordinateurs

Nous présentons ici un panorama sur l'arithmétique utilisée dans la conception de circuits. Nous commencerons par un survol des diverses évolutions de *l'arithmétique des ordinateurs* dans les dernières décennies, puis nous ferons une présentation sommaire des systèmes de représentations employés. Nous nous attacherons plus à leurs propriétés et à l'impact de celles-ci dans la conception de circuits numériques, qu'à définir les notations associées à chaque système.

## 1.1.1 Évolution de l'arithmétique dans les circuits numériques

La loi de Moore [Moor65], énoncée à la fin des années 60 [Moor65], tablait sur le quadruplement de la densité d'intégration des circuits tous les 3 à 4 ans. Jusqu'à présent cette loi s'est vérifiée. Cette augmentation de la densité d'intégration s'est accompagnée de l'augmentation de la complexité des applications intégrées et des cœurs de calculs utilisés. Ces évolutions ont donné lieu, entre autres, à un enrichissement graduel de l'arithmétique employée dans les semi-conducteurs.

Dans un premier temps, l'élargissement a porté sur les opérateurs disponibles. Initialement composé d'additionneur/soustracteur, les cœurs de calculs ont peu à peu pu intégrer la multiplication, la division, les fonctions logarithme, exponentielle ou trigonométriques comme le sinus, le cosinus ou la tangente. La progression des unités et coprocesseurs arithmétiques de la famille de processeurs 80X86 et Pentium de la société Intel illustre parfaitement ce propos.

La seconde évolution introduite par la diminution de la contrainte matérielle a porté sur l'évolution des techniques et algorithmes mis en œuvre pour câbler les opérations dans le silicium. Ceux-ci sont passés d'un traitement des données effectué en série (des chiffres les moins significatifs/LSB vers les chiffres les plus significatifs/MSB) et inversement (arithmétique en ligne), à un traitement effectué en parallèle. Conjointement, la dynamique des données a cru, passant de mots de 4, 8 bits dans les années 80 à des mots de 64 à 128 bits dans les années 1990. Si les arithmétiques séries ont été supplantées par l'arithmétique parallèle dans la conception d'ASIC, l'arithmétique en ligne (calcul du MSB vers le LSB), est encore exploitée dans les FPGA où les contraintes matériel disponible et routage, sont encore importantes. Il est intéressant de noter, qu'aussi bien pour l'arithmétique en ligne que pour l'arithmétique série (calcul du LSB vers le MSB) les traitements unitaires sont effectués par blocs de chiffres/bits. Les calculs peuvent alors être semi-parallèles.

Enfin un troisième type d'évolution a été rendue possible par l'augmentation de la densité d'intégration des circuits. Celui-ci correspond à l'emploi de nouveaux systèmes de représentations des nombres. En premier lieu l'introduction des notations flottantes a permis d'élargir l'espace des nombres utilisés des nombres entiers ou à virgule fixe aux nombres réels. En deuxième lieu, l'usage des notations redondantes et des notations par résidus a permis d'améliorer les performances en fréquences des opérateurs et des circuits réalisés. Nous reviendrons sur ces systèmes de représentations dans la sous-section 1.1.2.

Il est intéressant de noter que si la mise en œuvre de l'arithmétique dans les semi-conducteurs a été et est encore graduelle, de très nombreux concepts, problèmes et solutions ont été proposés et formalisés dans les années 1950/1960. C'est le cas des systèmes de représentations flottants [Camp92], des représentations par résidus [Garn59, Szab67] où des représentations redondantes [Metz59, Aviz62]. C'est aussi le cas pour les algorithmes utilisés pour câbler les opérations arithmétiques comme la multiplication [Dadd65, Wall64] ou les fonctions logarithme, exponentielle et trigonométriques CORDIC [Brig28, Vold59].

#### 1.1.2 Systèmes de représentations

Du point de vue de la conception de circuits numériques, les systèmes de représentations peuvent être séparés en deux types : ceux définissant une arithmétique autonome et les autres. Nous entendons par arithmétique autonome une arithmétique permettant de couvrir l'ensemble des besoins arithmétiques élémentaires tout en offrant des performances matérielles cohérentes et acceptables.

Le minimum nécessaire comprend les opérateurs basiques : un additionneur / soustracteur, un comparateur, un multiplieur et un diviseur, et les primitives élémentaires nécessaires au contrôle des calculs comme le signe, la valeur nulle et la détection de dépassement de capacité. La notion de contrôle évoquée ici n'est pas à confondre avec la notion de commande des calculs (soustraction/addition par exemple); nous parlons ici uniquement du contrôle des résultats des calculs.

Un coût à ne pas négliger dans l'évaluation d'un système de représentation, est celui de la taille des codages des nombres sur les opérations non arithmétiques comme la mémorisation ou les aiguillages (multiplexeurs/démultiplexeurs ou bus).

#### Systèmes de représentations définissant une arithmétique autonome

Dans un premier temps les nombres ont été représentés et manipulés sous forme d'une valeur entière signée ou non signée permettant de coder un nombre entier ou un nombre à virgule fixe; la position de la virgule étant définie arbitrairement en fonction de la dynamique des valeurs manipulées. Nous détaillerons les principales représentations correspondantes dans le chapitre 2. Pour fixer le lecteur, il s'agit de la *numération simple de position*, de la notation *signe et grandeur* et de la notation *en complément à la base*. Nous nous référerons à elles dans le reste de ce mémoire en parlant de notations ou de représentations *classiques* ou *conventionnelles*.

Très rapidement, et afin de représenter les nombres réels, les systèmes de représentations classiques ont été complétés par le développement des représentations des nombres à virgule flottante [Camp92, Yohe73, Cody73, Coon84, Gold91, Kaha96]. Ces travaux ont débouché sur un norme établi en 1985 [IEEE85].

Les flottants constituent une notation de plus haut que les systèmes déjà exploités où les nombres sont codés tel que  $Nombre = Mantisse * 2^{Exposant}$ ; Mantisse et Exposant sont des nombres classiques de taille fixe. Ces notations permettent d'étendre la représentation des nombres entiers ou à virgule fixe, aux nombres réels ou plutôt à virgule flottante. Cette extension s'est concrétisée par la dilatation de l'intervalle des nombres pouvant être codés sur une quantité N de bits donnés. Le nombre de codes possible reste toutefois de  $2^N$  comme pour un codage classique sur N bits. L'élargissement a été rendu possible par le passage de l'écart entre deux codes contigus, d'une valeur fixe pour les notations classiques à une valeur coefficientée par l'exposant pour les flottants. Aussi, sur un intervalle donné et pour N fixé, les flottants sont moins précis que les notations classiques. Pour obtenir une précision équivalente, la mantisse des flottants doit être égale à la taille de la notation classique correspondante.

Nous l'avons dit, les notations flottantes sont un sur-ensemble des notations classiques. Il en va de même pour les opérateurs arithmétiques associés [Mull89, Parh99]. Ceux-ci se composent

d'opérateurs arithmétiques classiques qui effectuent le traitement de l'opération proprement dite, et d'autres opérateurs arithmétiques classiques pour exécuter en parallèle le calcul du nouvel exposant. Certaines opérations comme l'addition nécessitent au préalable l'alignement des virgules. Cette dé-normalisation des nombres avant traitement implique une re-normalisation après calcul. Le coût des opérateurs flottants et donc plus élevé que celui des opérateurs classiques tant au plan de la vitesse de calcul que du matériel nécessaire.

Globalement les systèmes classiques et flottants définissent deux arithmétiques indépendantes et minimales. Celles-ci partagent les mêmes propriétés :

- 1. Toutes les opérations arithmétiques élémentaires comme l'addition, la soustraction, la multiplication la division ou les comparaisons sont réalisables sans recourir à d'autre systèmes de notations.

- 2. La détection des indicateurs d'états comme le signe, la valeur zéro ou le dépassement de capacité, est aisée, facilitant ainsi le contrôle des calculs.

- 3. Le codage d'un nombre est unique. Il est aussi compact. Les nombres négatifs peuvent être représentés.

Toutefois le coût plus important tant au niveau du codage des nombres que des opérateurs arithmétiques élémentaires, sont à l'origine de l'écartement des systèmes flottants des nombreuses applications où les contraintes de temps et de place (matériel) sont essentielles. Actuellement les flottants sont cantonnés à certains processeurs généraux ou DSP et à une utilisation logicielle plutôt que matérielle. Le fait que ces systèmes soient normalisés, peut aussi se révéler une contrainte dans leur réalisation matérielle.

Nos objectifs étant orientés vers la mise en place d'une arithmétique rapide, nous ne considérerons que les notations classiques dans la suite de ce mémoire.

#### Autres systèmes de représentations

Si les systèmes de représentations flottants sont exploités parce qu'ils permettent un élargissement de l'espace des nombres utilisables, d'autres systèmes sont eux employés afin d'améliorer les performances des blocs arithmétiques. Le premier objectif visé est de réduire le temps de calcul de l'addition qui est l'opération la plus élémentaire et la plus usitée. En circuiterie cela se traduit par la volonté de réduire la chaîne de propagation des retenues.

Les systèmes de représentations redondantes : *notations à retenues conservées* [Metz59] et *systèmes de nombres signés* [Aviz62], sont utilisés dans ce sens. Ces notations ont en point commun la particularité d'associer plusieurs codages à un même nombre. Cette particularité a permis

de restreindre la propagation des retenues de telle sorte que le calcul de l'addition est en temps constant [Aviz62, Mull89, Parh99]. Par comparaison le meilleur temps de calcul obtenu en utilisant les notations classiques, est en  $O(log_2(N))$  [Mull89, Parh99]. Nous reviendrons en détail sur ces systèmes dans le chapitre 2.

Une seconde famille de systèmes de représentations est employée dans le but d'améliorer les performances des circuits. Il s'agit des systèmes de représentations par résidus [Garn59, Szab67]. L'idée directrice est de découper les nombres en sous-ensembles indépendants. Pour se faire, on définit un ensemble  $M=\{m_1,m_2,...,m_N\}$  de N entiers, appelé la base. En assurant que tous les  $m_i$  sont premiers entre eux, chaque entier I tel que  $0 \le I < \prod_{i=1}^N m_i$ , est représentable par un unique N-tuple  $I_{RNS}=\{< I>_{m_1}, < I>_{m_2},..., < I>_{m_N}\}$ ;  $< I>_{m_i}$  correspond à I modulo  $m_i$ . Cette propriété acquise, les calculs s'effectuent parallèlement et indépendamment sur les divers sous-ensembles. Les temps de calculs sont alors réduits ainsi que le matériel requis pour la réalisation des opérateurs. Dans le cas de l'addition, le temps de propagation est en O(log(log(N))) [Parh99]. Le premier log correspond à la décomposition en sous-ensembles, le deuxième au meilleur résultat obtenu dans la conception d'un additionneur classique. Ces systèmes sont très intéressants car ils offrent aussi une réduction conséquente du temps de propagation et du matériel nécessaire au calcul de la multiplication [Parh99, Pali00]. Cette seconde opération est aussi essentielle que l'addition à la réalisation de circuits numériques.

L'introduction de ces nouveaux systèmes s'est d'abord faite dans la conception même des opérateurs. C'est le cas des notations redondantes qui sont employées dans la réalisation d'opérateurs comme les multiplieurs ou les diviseurs [Cava84, Mull97, Parh99]. Cet usage porte à la fois sur la réduction des chaînes de propagation des retenues dans les arbres d'additions [Wall64, Dadd65], et sur l'utilisation des propriétés des systèmes définis par Avizienis dans [Aviz62]. Dans ce second cas on peut citer comme exemples les multiplieurs parallèles de *Booth* [Boot51, Souf00] ou les multiplieurs par une constante [Aber95] et annexe A. Il est intéressant de noter que dans le cas des opérateurs incorporant une somme à la fin du calcul, le résultat est d'abord exprimé en notation redondante puis converti en notation classique. Le convertisseur n'est autre qu'un additionneur classique.

Plus récemment, l'augmentation de la complexité des applications visées a nécessité la conception de cœurs de calculs câblant le chaînage de plusieurs opérateurs arithmétiques. Ces enchaînements ont ouvert la voix à l'emploi explicite des systèmes de représentations redondantes et *RNS*. Nous entendons par *explicite* le fait que ces notations sont utilisées comme lien entre opérateurs.

Dans le cas des redondants, il s'agit d'éviter la phase de conversion de notation redondante

$\rightarrow$  classique présente à la fin de nombreux opérateurs comme les additionneurs/soustracteurs ou les multiplieurs. Il existe quelques exemples qui suivent cette direction. Briggs et Matula [Brig93] ont conçu un bloc effectuant une multiplication/accumulation (MAC) utilisé par le coprocesseurs Cyrix 83D87, dans laquelle le résultat de la multiplication n'est pas converti avant d'être accumulé. Un autre exemple très intéressant d'utilisation explicite des redondants, est proposé par Olivier Peyran qui, dans sa thèse [Peyr97], traite de l'introduction des notations redondantes dans la synthèse de haut niveau.

Les exemples d'utilisations des notations RNS portent essentiellement sur des cœurs de calculs très fortement arithmétique, incluant de multiples multiplications et additions, comme le calcul de la transformée cosinus discrète [Rami00] ou les filtres numériques [Conw00]. Cette particularité s'explique par le coût (en délai) assez élevé des conversions entre notations RNS et classiques [Parh99]. De nombreux travaux actuels traitent de ce problème [Soud00, Pali00] et cette contrainte tend à se réduire. Toutefois elle reste encore une limite à l'utilisation des RNS.

Le premier défaut majeur de ces deux systèmes de représentations, est de ne pas permettre une détection aisée (à moindre coût) des indicateurs de signe, de nullité et de dépassement de capacité, comme avec les représentations classiques ou flottantes. Cette difficulté est à l'origine d'une succession de problèmes et de limitations :

- 1. Sans indicateurs de contrôle les systèmes redondants et RNS ne définissent pas une arithmétique autonome. Ils doivent être utilisés conjointement avec une arithmétique autonome, généralement l'arithmétique classique. Des convertisseurs de format sont alors nécessaires. Leur coût est non nul et l'amélioration des performances apportée par l'usage des notations redondantes et RNS en est réduite.

- 2. La complexité des opérateurs dont l'algorithme est basé sur ces indicateurs, croît fortement ce qui est à l'origine de la dégradation ou de l'inversion du gain potentiellement introduit par les autres opérateurs. C'est le cas pour les opérateurs de division et de comparaison qui exploitent le signe de résultats partiels ou du résultat final. Le recours à des opérateurs définissant ces opérations dans d'autres systèmes de représentations est nécessaire.

- 3. Ces systèmes sont écartés des processeurs, et ne sont utilisables qu'à l'intérieur de blocs arithmétiques enchaînant des calculs sans contrôle des résultats. Dans le cas des notations redondantes ces blocs peuvent même être des opérateurs.

Le second défaut majeur de ces notations, est qu'elles ne sont pas compactes. L'augmentation de la taille des codages sous-entendue a un coût important sur les opérations non arithmétiques (mémorisation, multiplexeur, etc.). Pour une même dynamique et par rapport aux systèmes classiques, la taille des codages varie autour du double que ce soit pour les systèmes

#### Chapitre 1 1.2 Conception automatisée d'architectures / synthèse d'architectures

redondants [Mull89, Parh99] (*notations à retenues conservées* section 2.2) ou pour les *RNS*. Dans le cas de ces derniers l'augmentation dépend à la fois des modulos choisis et de la dynamique maximum des données que l'on souhaite traiter.

# 1.2 Conception automatisée d'architectures / synthèse d'architectures

Parallèlement à l'évolution de l'arithmétique dans la conception de circuits, la complexité croissante des applications visées et la durée de vie très courte des produits développés, impliquent le besoin de méthodes et d'outils d'aide à la conception. La combinaison de ces deux contraintes s'est traduite par un désengagement des techniques de conception *bas niveau* en faveur de l'automatisation du flot de conception d'architecture.

Schématiquement cette automatisation prend la forme d'outils d'aide à la conception décomposable en trois étapes successives. Les deux premiers opèrent respectivement au niveau de la spécification du système et de l'architecture. Les solutions mises en œuvre sont entre autres basées sur des modèles de transactions de données et des modèles comportementaux de blocs élémentaires comme les opérateurs arithmétiques. On parlera de *synthèse de systèmes* et de *synthèse de haut niveau*. Le troisième étage effectue lui, la traduction des modèles comportementaux en modèles structurels *bas niveau*.

Dans ce contexte, la conception d'un circuit est descendante et passe par plusieurs phases de raffinement. L'architecture obtenue est hiérarchique. Sa réalisation sera ascendante : des blocs de plus bas niveau vers les blocs de plus haut niveau.

## 1.2.1 Synthèse de système

L'objectif de la synthèse de systèmes, est de définir la répartition d'une application entre réalisation logicielle et matérielle. Cette réparation comprend trois parties. La première correspond à la synthèse logicielle et permet, par exemple, de définir le code exécutable pour un processeur. La deuxième correspond à la synthèse matérielle. Elle effectue indifféremment des appels à des ressources préexistantes (processeur, coprocesseur, RAM, etc.) ou en définit de nouvelle par un comportement et une technologie cible (FPGA, bibliothèque de portes logiques précaractérisées, blocs dur déjà câblés Full-Custom). La troisième partie effectue la synthèse des communications (bus, connexions, protocoles de transactions, etc.) permettant ainsi d'assurer le dialogue entre les diverses ressources.

À ce niveau, un système est constitué d'éléments décrits par des comportements (algorithmes) généralement de très haut niveau. Chacun de ces éléments correspond à un circuit numérique synchrone, la synchronisation étant assurée par une ou plusieurs horloges. Par la suite, chaque

description comportementale va être traduite en une description structurelle implantant les parties de contrôle et les parties opératives des algorithmes.

#### 1.2.2 Synthèse de haut niveau

Cette seconde étape a pour rôle de traduire un circuit, décrit par un comportement haut niveau (algorithme) en une description sous forme de transferts de registres (RTL). Un des objectifs est de dissocier la partie opérative de la partie de contrôle.

Cette étape est décomposable en 4 phases : l'extraction des graphes de dépendances de contrôles et de données à partir de l'algorithme, la sélection du type des ressources (opérateurs), l'ordonnancement des opérations et l'allocation de ressources.

Classiquement deux types d'ordonnancements sont effectués : l'ordonnancement sous contraintes de ressources où les ressources sont fixées et où l'objectif est de minimiser le temps en cycles d'horloges, et l'ordonnancement sous contraintes de temps où le nombre de cycles d'horloge est fixé et où l'objectif est de minimiser les ressources. L'ordre d'enchaînement des trois dernières étapes n'est pas figé. La solution généralement adoptée consiste à sélectionner le type des opérateurs, puis à effectuer l'ordonnancement et l'allocation de ressource.

La traduction sous forme de *transferts de registres* s'appuie sur un ensemble de ressources dont on connaît le comportement et les performances, comme les opérateurs arithmétiques, les multiplexeurs, les bus ou les registres. Ces derniers sont synchronisés par une horloge. À travers ces ressources, il est tenu compte de la technologie cible choisie : portes logiques précaractérisées FPGA ou Full-Custom.

À ce point, on sait sur quel opérateur et à quel cycle d'horloge, chaque opération de l'algorithme est exécutée. De même, on sait quel registre va être affecté par une variable. La structure de la partie opérative est connue. On peut alors facilement extraire de cette description, un organigramme de contrôle dont les états sont les opérations RTL. La partie contrôle est aussi connue.

Globalement la structure du circuit est définie. Chaque élément des parties *opérative* et *contrôle* ainsi que leurs interconnexions sont décrites, par exemple sous forme d'équations booléennes. Pour la partie opérative, ces descriptions s'arrête au niveau des ressources. En effet, bien que les propriétés (comportements) de celles-ci aient été utilisées lors des phases de définition et d'allocation des opérateurs, leurs structures ne sont pas forcément connues. Ce niveau de raffinement permet de réduire la complexité de la synthèse de haut niveau.

Deux types d'outils ont été développés pour réaliser la synthèse de haut niveau. Dans les premiers tous les mécanismes de décisions (choix opérateurs,...) sont intégrés. Nous parlerons de synthèse globale. Dans les seconds le choix et l'allocation des ressources sont définis par l'utili-

#### Chapitre 1 1.2 Conception automatisée d'architectures / synthèse d'architectures

sateur via la description de la partie opérative sous forme de *chemin de données*. La construction de la partie contrôle est obtenue, elle, par synthèse de haut niveau. Elle est basée sur la description haut niveau du circuit, sur la description de la partie opérative et sur les performances des ressources utilisées. Ces outils définissent un sous-ensemble des premiers.

Cette approche *synthèse de partie contrôle* a été retenue dans divers outils *HUGH* actuellement développé au sein de notre laboratoire [Augé97, Augé99].

Sur le plan arithmétique et jusqu'à récemment, cette étape de la synthèse d'architecture ne prenait en compte que les notations et les opérateurs classiques. Dans sa thèse [Peyr97], Olivier Peyran propose d'intégrer en plus, les systèmes de notations redondants. Ces travaux novateurs ont montré la faisabilité et l'intérêt d'utiliser plusieurs systèmes de représentations simultanément.

#### 1.2.3 Synthèse au niveau transfert de registres (RTL)

Ce dernier étage effectue la traduction de la description RTL en description structurelle bas niveau; c'est à dire la transformation des équations logiques et des ressources en un réseau de cellules élémentaires interconnectées. Suivant la technologie cible, les cellules élémentaires sont des portes logiques précaractérisées (bibliothèques de portes), des blocs *durs optimisés* (Full - Custom) ou des CLB (FPGA).

Deux approches sont possibles pour réaliser la synthèse RTL: l'approche dominée par le contrôle et l'approche généralisée. Dans la première, le circuit est découpé en une partie opérative (chemin de données) et une partie de contrôle (contrôleur) synthétisées séparément. Dans la seconde, le circuit est considéré dans son ensemble, le contrôle est alors intégré dans chaque bloc du graphe de dépendance de contrôle de départ. Les outils de synthèse adoptent généralement l'approche dominée par le contrôle.

Dans les deux cas, la synthèse RTL se décompose en deux phases. Une phase de traduction en équations logiques des ressources, de la connectique et du contrôle et une phase de projection (mapping). Ces phases font appel à la synthèse de contrôleurs, à la synthèse logique et à l'exploitation de générateurs encapsulant un savoir-faire (Intellectual-Property / IP).

#### Synthèse logique ou synthèse bas niveau

L'objectif de la synthèse logique est de convertir les équations logiques définies lors de la synthèse RTL en une description minimale en termes de cellules élémentaires. La notion de *minimale* peut-être raccrochée à plusieurs critères comme la consommation, la quantité et la taille des cellules élémentaires (surface) et le temps de propagation du bloc obtenu.

Cette synthèse est décomposable en deux étapes distinctes. La première correspond à l'optimisation booléenne des équations logiques. Le but est entre autres d'éliminer la redondance des équations (partage de partie d'équation commune), de les simplifier via leur substitution par des équations *logiquement* identiques mais moins coûteuses en matériel. La seconde a pour rôle la projection (*mapping*) des nouvelles équations optimisées sur la cible technologique souhaitée. Il s'agit ici de découper les équations en fonctions des possibilités (disponibilité, complexité des cellules) et des qualités (surface, délai, consommation) offertes par les cellules élémentaires.

Les deux principaux avantages de la synthèse logique sont la facilité d'utilisation et la portabilité qu'elle offre. La facilité car c'est une approche *presse-bouton* et les langages de description sont normalisés : VHDL et Verilog par exemple. La portabilité car avec la même description haut niveau il est possible de changer de cible technologique.

Le revers de la médaille vient de la difficulté de synthétiser les ressources arithmétiques. En effet, la synthèse ne peut pas/ne sait pas tirer parti des structures régulières, de la variabilité (taille entrée/sortie, algorithmes), et de la forte corrélation des équations logiques internes à ces blocs.

Ce problème est encore d'actualité et il se retrouve dans les outils commerciaux comme Synopsys [SYN00]. Une des solutions adoptées consiste à remplacer la synthèse d'un opérateur arithmétique par l'appel, de façon transparente, à un générateur de l'opération souhaitée, celuici fournissant directement les équations à projeter.

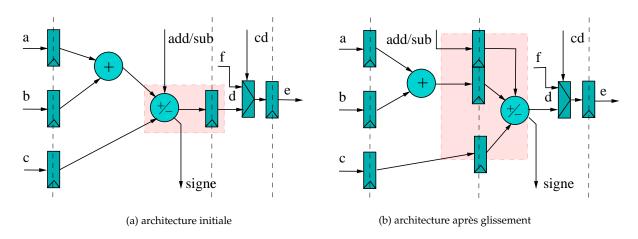

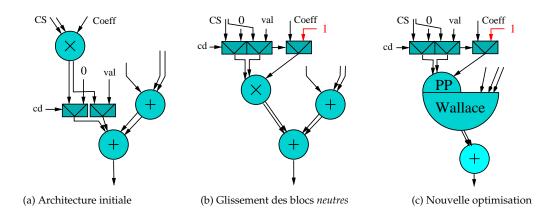

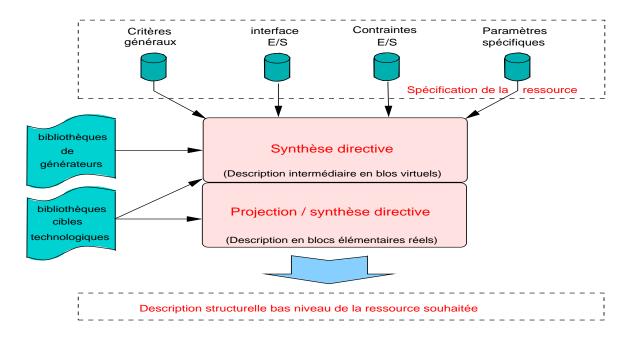

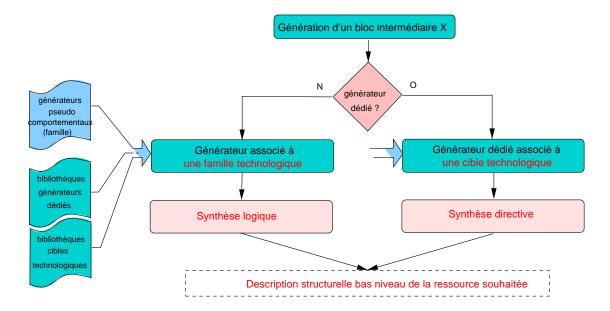

#### Générateurs et chemin de données