## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PARIS VI

SPÉCIALITÉ INFORMATIQUE

Présentée par François DONNET

Pour obtenir le titre de

DOCTEUR DE L'UNIVERSITÉ PARIS VI

## Synthèse de Haut Niveau Contrôlée par l'Utilisateur

Soutenue le 20 janvier 2004, devant le jury composé de

| Mr Ahmed JERRAYA   | Rapporteur         |

|--------------------|--------------------|

| Mr Eric Martin     | Rapporteur         |

| Mr Alain GREINER   | Examinateur        |

| Mr Henri MICHEL    | Examinateur        |

| Mr Frédéric PÉTROT | Examinateur        |

| Mr Tanguy RISSET   | Examinateur        |

| Mr Ivan AUGÉ       | Directeur de thèse |

## **Avant-propos et remerciements**

Cette thèse a été effectuée dans le Laboratoire d'Informatique de Paris VI au département Architecture des Systèmes Intégrés et Micro-électronique dirigé par Alain Greiner, Professeur à l'Université Paris VI.

Je tiens à remercier particulièrement Ivan Augé, Maître de Conférence, enseignant à l'Institut d'Informatique d'Entreprise à Evry, qui a dirigé mes recherches. Il a toujours été disponible malgré l'éloignement et a constamment suivi mes travaux. Je tiens à le remercier pour sa relecture attentive de ce manuscrit ainsi que ses conseils avisés. Son soutien m'a été d'une aide plus que précieuse.

J'adresse mes remerciements à Ahmed Amine Jerraya et Eric Martin qui m'ont fait l'honneur d'être les rapporteurs de ma thèse, ainsi qu'à l'ensemble des membres du jury.

Je remercie l'ensemble des membres du département ASIM avec qui j'ai eu des échanges fructueux. J'ai eu un grand plaisir à travailler au sein de l'équipe SoC menée par Frédéric Pétrot. Il m'a fait bénéficier de sa large expérience couvrant tous les domaines de la micro-électronique. Il a de plus contribué pour une part non négligeable à notre outil de synthèse de haut niveau *ugh*.

J'ai aussi une pensée particulière pour les premiers utilisateurs de notre outil de synthèse Mouhamadou Diaby, Etienne Faure, Jean-Baptiste Lhomme et Mathieu Tuna. Bien qu'ils aient eu leurs propres échéances à tenir, leur patience et leur tolérance ont été appréciables. De plus, ils ont soulevé des questions avant qu'elles ne deviennent des problèmes.

Je remercie le Laboratoire d'Électronique des Systèmes Temps Réels (LESTER), pour m'avoir permis d'utiliser l'outil de synthèse *gaut* et plus particulièrement, Pierre Bomel, pour avoir répondu de façon très réactive à mes questions incessantes sur leur outil.

Enfin, j'ai une pensée particulière pour Fabienne Cori qui m'a soutenu pendant ces trois années.

## Résumé

La synthèse de haut niveau de coprocesseur dédié est un problème complexe. Elle doit répondre à différents objectifs tels que la fréquence de fonctionnement, la surface, la consommation, etc... Ces critères caractérisent le circuit généré et donc l'efficacité de l'outil de synthèse de haut niveau.

Cette thèse présente une approche en deux étapes de la synthèse de haut niveau.

Dans un premier temps, on s'intéresse à minimiser la surface et à maximiser le parallélisme.

Dans un deuxième temps, le circuit est ajusté pour prendre en compte les caractéristiques électriques du matériel et produire un circuit fonctionnant à la fréquence désirée.

L'outil de synthèse peut donc se concentrer sur l'optimisation d'un nombre réduit de caractéristiques visées par le concepteur.

Cependant, pour les circuits dont le contrôle dépend des données, l'objectif ne peut pas être caractérisé par une directive globale car une telle directive est inadaptée et ne permet pas de qualifier le degré d'optimisation à atteindre. Les répercussions sur les autres caractéristiques du circuit ne sont pas contrôlées par le concepteur.

Le respect de la directive globale est difficilement tenable par les algorithmes de synthèse. Les phases d'ordonnancement, d'allocation et d'affectation nécessaires à la synthèse de haut niveau possèdent une complexité non polynomiale. Elles se résolvent la plupart du temps par des heuristiques qui ont des conséquences imprédictibles sur les caractéristiques du circuit généré.

L'automatisation de la synthèse de haut niveau passe par une description précise des attentes du concepteur. Nous étudions dans cette thèse les directives nécessaires pour cibler précisément une solution et rester compatibles avec notre démarche en deux phases de la synthèse. Il faut que la définition de ces directives soit la moins contraignante possible pour le concepteur, tout en étant attentif à la perte d'efficacité qu'engendre leur simplification.

**Mots clefs :** synthèse de haut niveau, coprocesseur dédié, fréquence de fonctionnement, surface, parallélisme, contrôle dépendant des données, ordonnancement, allocation, affectation, microarchitecture, circuit intégré.

## **Abstract**

The high level synthesis for dedicated coprocessor is a very complex problem. It has to cope with different aims like the working frequency, the surface, the consumption, etc...

These criteria specify the generated circuit and the high level synthesis tool efficiency.

This Ph.D thesis presents a two steps approach in the high level synthesis.

In the first step, we minimize the surface and maximize the parallelism.

In the second step, the circuit is modified to take in account the electrical characteristics and to fetch the wanted working frequency.

The synthesis tool has to optimize the circuit on a very few number of criteria which are specified by the designer.

By the way, for the data control dominated circuits, the aim can't be qualified by a global guidance, because a such guidance is unadapted and can't qualify the optimization level. The collateral effects on the other characteristics of the circuit aren't controlled by the designer.

The respect of the global guidance is difficult to reach by the synthesis algorithms. The scheduling, allocation and binding phases of the high level synthesis are NP-complex. Most of these problems are solved with heuristics which have unpredictable consequences on the circuit characteristics.

The automation of the high level synthesis needs a very precise description of the designer's attempts. We are studying in this Ph.D thesis the necessary guidances to precisely aim a solution and keep the compatibility with our two-phases approach. We have to reduce the guidance definition to facilitate the designer's work and be aware of the loss of efficiency which has been induced.

**Keywords:** high level synthesis, dedicated coprocessor, working frequency, surface, parallelism, data control dominated, scheduling, allocation, binding, micro-architecture, integrated circuit.

## Table des matières

| 1 Introduction |      |                                                                             |    |  |  |  |

|----------------|------|-----------------------------------------------------------------------------|----|--|--|--|

|                | 1.1  | Plan du manuscrit                                                           | 14 |  |  |  |

| 2              | Prol | Problématique                                                               |    |  |  |  |

|                | 2.1  | La synthèse                                                                 | 16 |  |  |  |

|                | 2.2  | La synthèse de haut niveau                                                  | 19 |  |  |  |

|                | 2.3  | Les principes de la synthèse de haut niveau                                 | 22 |  |  |  |

|                | 2.4  | Les problèmes ouverts                                                       | 27 |  |  |  |

|                | 2.5  | Conclusion                                                                  | 31 |  |  |  |

| 3              | État | de l'art                                                                    | 33 |  |  |  |

|                | 3.1  | Les algorithmes d'ordonnancement                                            | 34 |  |  |  |

|                | 3.2  | Les algorithmes d'affectation                                               | 37 |  |  |  |

|                | 3.3  | Les outils de synthèse haut niveau                                          | 40 |  |  |  |

|                | 3.4  | Conclusion                                                                  | 48 |  |  |  |

| 4              | Mét  | hode logicielle pour tenir compte des contraintes électriques               | 51 |  |  |  |

|                | 4.1  | Les contraintes électriques                                                 | 54 |  |  |  |

|                | 4.2  | La prise en compte des contraintes électriques par la synthèse classique    | 57 |  |  |  |

|                | 4.3  | La prise en compte des caractéristiques électriques dans la synthèse ciblée | 62 |  |  |  |

|                | 4.4  | Le respect des contraintes électriques dans la synthèse ciblée              | 65 |  |  |  |

|                | 4.5  | Conclusion                                                                  | 73 |  |  |  |

| 5              | Cibl | er une solution                                                             | 75 |  |  |  |

|                | 5.1  | L'espace des solutions                                                      | 77 |  |  |  |

|                | 5.2  | Les directives nécessaires pour cibler une solution                         | 86 |  |  |  |

|   | 5.3 Exemples de directives dans la synthèse ciblée                 | <br>94  |

|---|--------------------------------------------------------------------|---------|

|   | 5.4 Conclusion                                                     | <br>98  |

| 6 | Obtention rapide d'une solution                                    | 99      |

|   | 6.1 L'ordonnancement dans la synthèse classique                    | <br>101 |

|   | 6.2 L'ordonnancement dans la compilation logicielle                | <br>104 |

|   | 6.3 L'ordonnancement avec l'affectation fixée des registres        | <br>106 |

|   | 6.4 L'ordonnancement dans la synthèse ciblée                       | <br>109 |

|   | 6.5 Les points clefs de l'algorithme d'ordonnancement              | <br>115 |

|   | 6.6 Conclusion                                                     | <br>125 |

| 7 | Résultats et performances                                          | 127     |

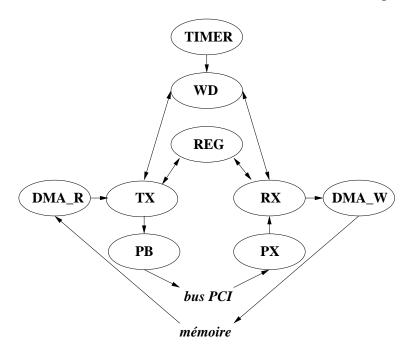

|   | 7.1 Les réalisations avec la synthèse ciblée                       | <br>129 |

|   | 7.2 La comparaison avec d'autres outils de synthèse                | <br>136 |

|   | 7.3 La couverture de l'espace des solutions                        | <br>142 |

|   | 7.4 L'intégration de la synthèse ciblée dans le flot de conception | <br>148 |

|   | 7.5 Les perspectives d'amélioration                                | <br>154 |

|   | 7.6 Conclusion                                                     | <br>157 |

| 8 | Conclusions et perspectives                                        | 159     |

|   | 8.1 Les objectifs atteints par la synthèse ciblée de haut niveau   | <br>160 |

|   | 8.2 Les perspectives                                               | <br>162 |

|   | Liste des figures                                                  | 165     |

|   | Glossaire                                                          | 169     |

|   | Bibliographie                                                      | 173     |

|   | Annexes                                                            | 177     |

| A | Langages de description comportementale utilisés                   | 177     |

|   | A.1 Le langage utilisé par <i>ugh</i>                              | <br>177 |

|   | A.2 Le langage utilisé par CoCentric/CoWare                        | <br>181 |

|   | A.3 Le langage utilisé par <i>gaut</i>                             | <br>185 |

|       |     |       |            |                                    | •            |  |

|-------|-----|-------|------------|------------------------------------|--------------|--|

|       | TOT |       | <b>DES</b> | 78 AF A F                          | $\mathbf{r}$ |  |

| 1 · A | K.  | и.    |            | <b>IX</b> / <b>II</b> / <b>X</b> · |              |  |

| -     |     | 1 1 1 | 7 1 1 1 1  |                                    |              |  |

|       |     |       |            |                                    |              |  |

| 1 | 1 |

|---|---|

| 1 | 1 |

|   |   |

| В | Dire                     | ctives d'affectations de la synthèse ciblée | 189 |  |  |  |

|---|--------------------------|---------------------------------------------|-----|--|--|--|

|   | B.1                      | La description des directives d'affectation | 189 |  |  |  |

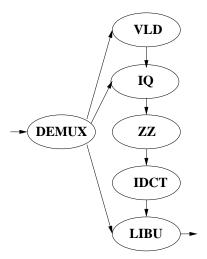

|   | B.2                      | L'exemple du vld                            | 189 |  |  |  |

| C | C Génération du VHDL RTL |                                             |     |  |  |  |

|   | C.1                      | La description VHDL RTL $n^o1$              | 191 |  |  |  |

|   | C.2                      | La description VHDL RTL $n^o2$              | 193 |  |  |  |

|   | C.3                      | La description VHDL RTL $n^o 3$             | 197 |  |  |  |

## Chapitre 1

## Introduction

ans le domaine de la conception assistée par ordinateur de circuits intégrés, l'intérêt porté à la synthèse de haut niveau réside essentiellement dans la réduction des temps de conception des circuits [Cam96]. La synthèse de haut niveau automatise certaines tâches de la conception.

L'une des évolutions récentes du flot de conception est l'utilisation systématique des outils de synthèse. La synthèse de haut niveau consiste à traduire une description comportementale séquentielle comme un programme en langage 'C' ou en 'PASCAL' en un circuit intégré.

Les performances d'un circuit à l'intérieur d'un système intégré sont difficilement évaluables autrement que par la simulation du système. Il faut donc construire un modèle au niveau matériel pour pouvoir évaluer le circuit dans son contexte. Le concepteur doit pouvoir tenter plusieurs architectures matérielles de son circuit afin de pouvoir choisir le rapport entre les performances et le coût de son circuit. Cependant les temps de conception "à la main" deviennent rédhibitoires car ils entraînent un coût d'ingénierie très important. Seule l'automatisation de la synthèse peut amener à une solution en un temps raisonnable. La synthèse de haut niveau facilite le travail d'exploration architecturale puisqu'elle accélère la production d'essais successifs pour un circuit.

A ce jour des résultats satisfaisants ont été obtenus pour des domaines d'application spécifiques comme le traitement du signal. En revanche, les outils de synthèse de haut niveau non spécialisés ne sont pas encore opérationnels pour des circuits complexes. La raison essentielle réside dans la faiblesse de ces outils à prendre en compte les contraintes temporelles ou structurelles du cahier des charges du circuit. Le concepteur ne peut décider des performances de son circuit.

Dans notre laboratoire *LIP6/ASIM*, un outil de synthèse de haut niveau a été développé. Il permet à l'utilisateur de spécifier des contraintes structurelles et temporelles du circuit.

Notre expérience avec cet outil sur des réalisations complexes nous a montré que des recherches doivent être menées pour étendre son champ d'application :

- 1. la description des contraintes structurelles est lourde pour l'utilisateur, alors qu'un bon nombre d'entre elles pourraient être déduites automatiquement;

- 2. l'absence de contraintes temporelles ferme les portes de tout une classe de circuits, en particulier les circuits synchrones.

ugh (User Guided High level synthesis) est l'outil de synthèse de haut niveau sur lequel nous allons

14 Introduction

réaliser les expérimentations. Il fait partie d'un ensemble d'outils d'aide à l'exploration architecturale appelé *DiSyDEnt* (Digital System Design Environment [ADG<sup>+</sup>02]) développé au laboratoire *LIP6/ASIM*.

#### 1.1 Plan du manuscrit

Le chapitre 2 présente les différentes phases de la synthèse de haut niveau et leur complexité. Il définit le cadre et les objectifs de cette thèse.

Le chapitre 3 présente de façon critique les approches classiques de la synthèse de haut niveau ainsi que les outils existants.

Le chapitre 4 est la présentation globale de la méthode logicielle utilisée par notre outil de synthèse de haut niveau. Cette méthode permet de s'affranchir des contraintes temporelles inhérentes à la synthèse et de simplifier la problématique.

Dans le chapitre 5, nous comparons les directives structurelles que le concepteur peut donner à l'outil de synthèse. Nous choisissons les plus efficaces et les plus adaptées à notre méthode logicielle.

Le chapitre 6 présente les algorithmes utilisés par notre outil de synthèse de haut niveau.

Le chapitre 7 présente les résultats expérimentaux. Il compare les résultats obtenus par la méthode développée dans cette thèse à d'autres approches existantes.

Enfin dans le chapitre 8, nous dressons le bilan des travaux effectués et quelques perspectives de recherche.

# Chapitre 2

## Problématique

## Sommaire

| 2.1 | La synthèse |                                                                             |    |  |

|-----|-------------|-----------------------------------------------------------------------------|----|--|

|     | 2.1.1       | Conception de circuit assistée par ordinateur                               | 16 |  |

|     | 2.1.2       | Descriptions comportementales                                               | 18 |  |

| 2.2 | La syı      | nthèse de haut niveau                                                       | 19 |  |

|     | 2.2.1       | Définition de la synthèse de haut niveau                                    | 19 |  |

|     |             | Les applications visées                                                     | 20 |  |

|     |             | Les entrées et les sorties de la synthèse                                   | 20 |  |

|     |             | Exploration de l'espace des solutions                                       | 20 |  |

|     | 2.2.2       | Environnement du coprocesseur                                               | 21 |  |

|     |             | Communications fonctionnelement asynchrones                                 | 22 |  |

|     |             | Fréquence d'horloge                                                         | 22 |  |

| 2.3 | Les p       | rincipes de la synthèse de haut niveau                                      | 22 |  |

|     | 2.3.1       | Phases de la synthèse de haut niveau                                        | 22 |  |

|     |             | Élaboration du graphe de flot de données et de contrôle                     | 23 |  |

|     |             | L'ordonnancement                                                            | 24 |  |

|     |             | Allocation matérielle                                                       | 24 |  |

|     | 2.3.2       | Cercles vicieux de la synthèse                                              | 25 |  |

|     |             | Échapper aux cercles vicieux                                                | 26 |  |

|     | 2.3.3       | Multiplicité et antagonisme des objectifs                                   | 26 |  |

|     |             | Échapper à la multiplicité des objectifs                                    | 26 |  |

| 2.4 | Les p       | roblèmes ouverts                                                            | 27 |  |

|     | 2.4.1       | Comment restreindre l'espace des solutions ?                                | 27 |  |

|     | 2.4.2       | Qu'apporte la connaissance des registres sur l'algorithme de la synthèse? . | 28 |  |

|     | 2.4.3       | Quelle formes ont les communications externes ?                             | 29 |  |

|     | 2.4.4       | Comment prendre en compte les caractéristiques électriques du circuit ?     | 29 |  |

|     | 2.4.5       | Comment interfacer l'outil de synthèse haut niveau avec les outils de       |    |  |

|     |             | synthèse RTL?                                                               | 29 |  |

| 2.5 | Concl       | usion                                                                       | 31 |  |

e chapitre a pour objet de poser les problèmes abordés dans cette thèse. Il traite des problèmes rencontrés aujourd'hui lors de la synthèse de haut niveau dans le domaine des circuits intégrés.

Les outils de synthèse de haut niveau ne sont pratiquement pas utilisés dans le domaine industriel. Ils ne répondent pas aux attentes des concepteurs. Car dans la plupart des cas, les circuits issus de la synthèse ne respectent pas les objectifs de performance.

La synthèse de haut niveau est un problème très complexe. L'outil de synthèse doit prendre beaucoup de décisions et respecter de nombreuses contraintes pour produire un résultat acceptable. Nous pensons que la synthèse de haut niveau est un problème trop complexe pour être totalement automatisé, et nous proposons une méthode qui permet au concepteur d'aider l'outil de synthèse dans ses décisions.

L'outil *ugh* (User Guided High level synthesis) développé au laboratoire *LIP6* est un outil de synthèse de haut niveau produisant des coprocesseurs spécialisés. *ugh* oblige le concepteur à donner des directives pour réduire le nombre de décisions et simplifier le travail de l'outil de synthèse. Le résultat de la synthèse est un circuit respectant les contraintes données par le concepteur.

Nous utiliserons l'outil *ugh* pour tester expérimentalement la validité de la méthode de synthèse de haut niveau proposée dans cette thèse.

Tout d'abord, il s'agit de positionner la synthèse de haut niveau telle que nous la voyons dans le flot de conception et d'identifier le domaine auquel elle est destinée. Nous verrons les difficultés de la synthèse de haut niveau d'un point de vue général. Pour les résoudre, ugh doit disposer d'un certain nombre d'informations que nous énumérerons. Nous nous poserons la question de la nature de ces informations et ce qu'elles modifient dans la méthode de synthèse de haut niveau. Enfin, nous nous demanderons comment intégrer de manière efficace le résultat de la synthèse dans le flot de conception.

### 2.1 La synthèse

### 2.1.1 Conception de circuit assistée par ordinateur

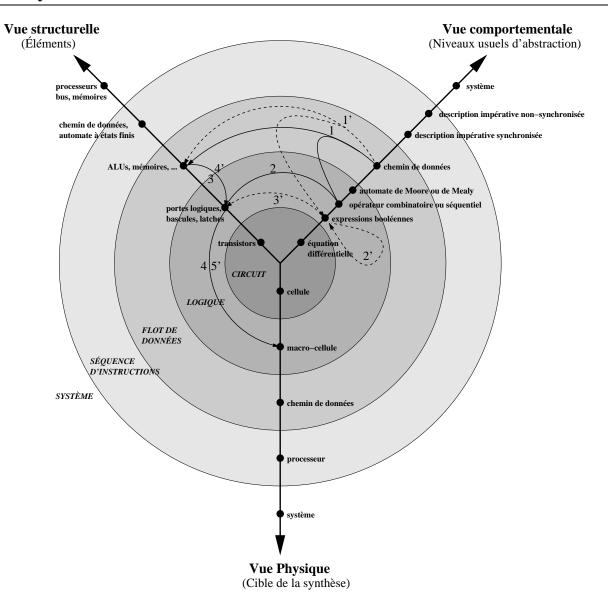

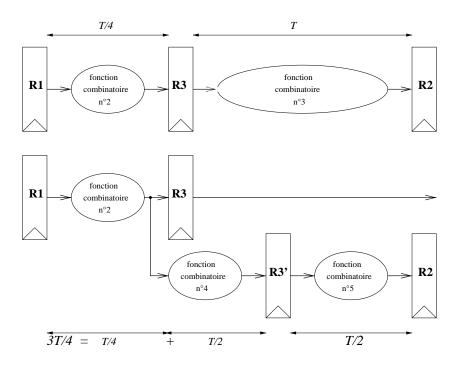

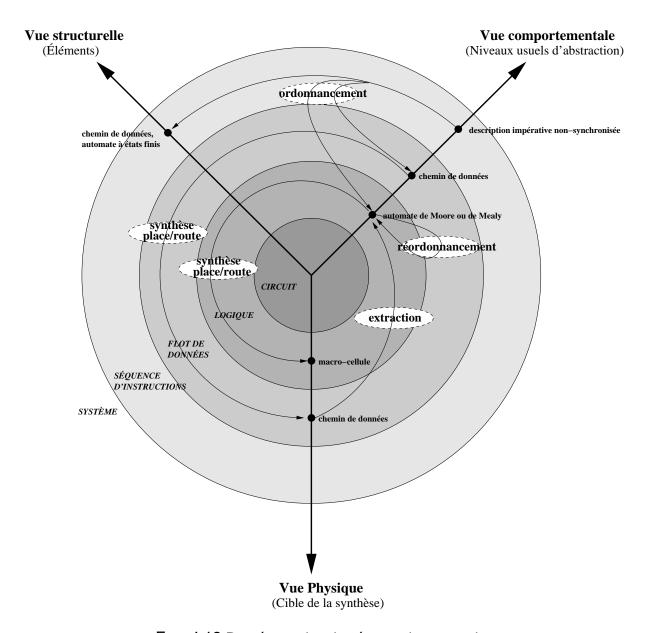

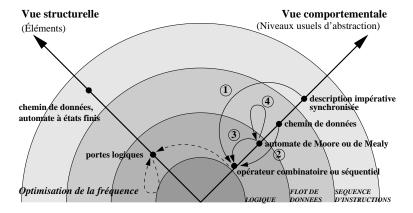

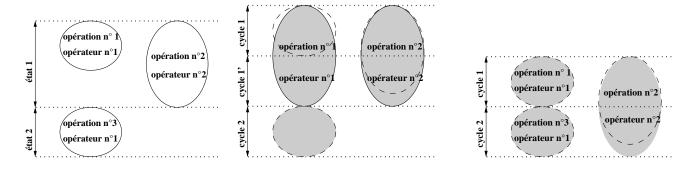

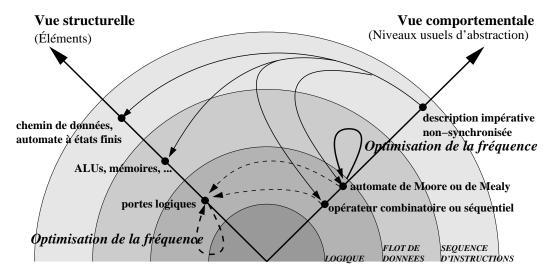

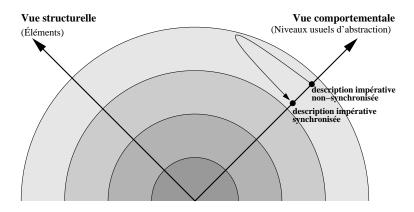

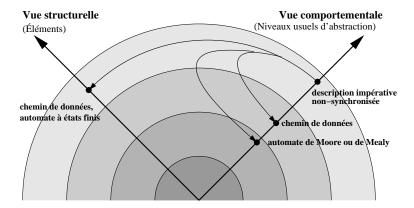

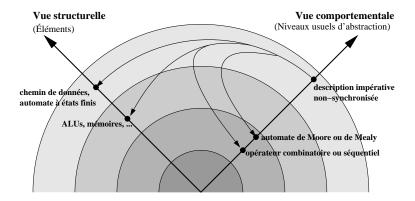

Pour définir la synthèse de haut niveau (HLS), nous nous basons sur le schéma de la figure 2.1 inspiré du *schéma en Y de Gajski* [HG85] [RKG<sup>+</sup>92]. Sur la figure, les cercles concentriques représentent des niveaux d'abstraction croissant du centre vers l'extérieur :

- ⇒ Circuit : conception d'une cellule à partir de transistors.

- ⇒ Logique : conception d'une macro-cellule à partir de transistors.

- ⇒ Flot de données : conception d'un chemin de données à partir de macro-cellules.

- ⇒ Séquence d'instructions : conception d'un coprocesseur à partir d'un chemin de données et d'une macro-cellule (i.e l'automate à états finis).

- ⇒ Système : conception d'une application à partir de coprocesseurs et de macro-cellules (bus, RAM, ...).

Les trois axes du Y représentent trois vues différentes d'un circuit. La vue comportementale donne la fonctionnalité du circuit. La vue structurelle indique les éléments qui composent le circuit. La

2.1 La synthèse

FIG. 2.1 Deux différents flots de conception.

vue physique contient les masques de fabrication du circuit. Les points sur les axes donnent les représentations usuelles des circuits introduites par les méthodes de conception.

La figure 2.1 permet de représenter les outils de conception assistée par ordinateur (CAO) de circuit. Les outils effectuent des transformations permettant de passer d'un point à un autre point (potentiellement le même). Ces transformations sont représentées par des arcs. Par exemple, l'*arc* 4 représente un outil de placement/routage de cellules, l'*arc* 3 représente une mise à plat d'une ALU en portes logiques et l'*arc* 2' une optimisation booléenne.

Ce schéma permet de visualiser les différents chaînages d'étapes (les arcs) menant de la vue comportementale à la vue physique (les points sur les axes).

Voici deux exemples de flot de conception, qui, partant d'un chemin de données et arrivant à une vue physique, passent par des étapes intermédiaires différentes :

1. Dans cet exemple, les transformations sont représentées par des arcs pleins dans la figure 2.1. L'étape 1 produit une vue structurelle avec des instances comportementales d'opérateurs. La forme en hyper-arc de l'arc 1 symbolise la production conjointe de la description structurelle d'opérateurs et des descriptions comportementales des opérateurs instanciés. Chaque comportement d'opérateur est synthétisé séparément en une vue structurelle de portes logiques grâce à l'étape 2. La vue structurelle d'opérateurs est mise à plat (arc 3) pour obtenir une vue structurelle au niveau portes de notre chemin de données entier. Le chemin de données est placé et routé de manière globale par l'étape 4.

2. Dans cet exemple, les transformations sont représentées par des arcs en pointillés dans la figure 2.1.

L'étape 1' produit une vue structurelle dont les feuilles sont des descriptions comportementales exprimées uniquement sous la forme d'expressions booléennes. L'étape 2' représente l'optimisation booléenne de ces expressions afin d'en réduire, par exemple, le nombre de littéraux. Les expressions booléennes sont synthétisées en portes logiques (arc 3'). La vue structurelle est mise à plat lors de l'étape 4' pour pouvoir placer et router l'ensemble grâce à l'étape 5'.

#### 2.1.2 Descriptions comportementales

La figure 2.1 introduit de nouveaux niveaux de description par rapport au schéma en Y de Gajski pour différencier les différentes étapes et algorithmes de la synthèse. Ceux-ci sont généralement pris en compte par un même outil et sont donc masqués pour l'utilisateur.

- L'équation différentielle donne le comportement électrique de la cellule.

- Les expressions booléennes sont un flot d'assignations concourantes exclusivement composées de fonctions booléennes.

- L'opérateur est soit combinatoire soit séquentiel. Il est décrit sous la forme d'un flot d'assignations concourantes à l'aide de fonctions arithmétiques et booléennes.

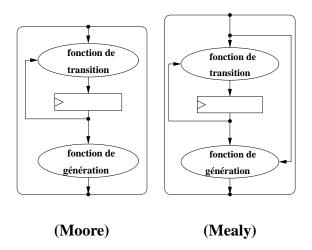

- L'automate de Moore ou de Mealy est une description d'automate à états finis. Un automate étant défini par :

soient

$\mathcal{E}$ : l'ensemble fini des états de l'automate,

$\mathcal{I}$ : l'ensemble fini des entrées de l'automate,

S: l'ensemble fini des sorties de l'automate.

On définit la *fonction de transition* de l'automate telle que  $\mathcal{E} \otimes \mathcal{I} \longmapsto \mathcal{E}$ .

On définit la fonction de génération de l'automate de Moore telle que  $\mathcal{E} \longmapsto \mathcal{S}$ .

On définit la *fonction de génération* de l'automate de Mealy telle que  $\mathcal{E} \otimes \mathcal{I} \longmapsto \mathcal{S}$ .

- Le chemin de données est un flot d'assignations concourantes. Il comporte des opérateurs séquentiels, arithmétiques, logiques...

- La description impérative est une description procédurale comme les langages Pascal, C ou Ada.

- Dans la description synchronisée, les frontières de cycles sont données. La *fonction de transition* est donc connue.

- Dans la description non synchronisée, les frontières de cycles ne sont pas données.

- Le système représente le traitement complet d'une ou plusieurs tâches et les échanges de données nécessaires entre les différents éléments d'un système.

Dans la littérature, la description impérative synchronisée et le chemin de données sont des descriptions de niveau transferts de registres (RTL). Dans ces descriptions, les registres, les opérations fonctionnelles qui leurs sont assignées, ainsi que le cycle dans lequel elles sont faites, sont déjà identifiés.

### 2.2 La synthèse de haut niveau

#### 2.2.1 Définition de la synthèse de haut niveau

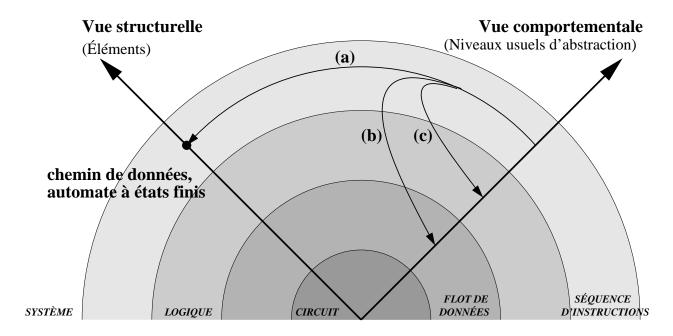

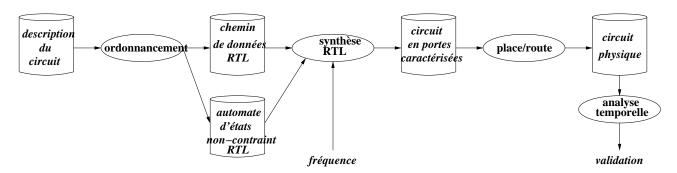

FIG. 2.2 La synthèse de haut niveau dans le flot de conception.

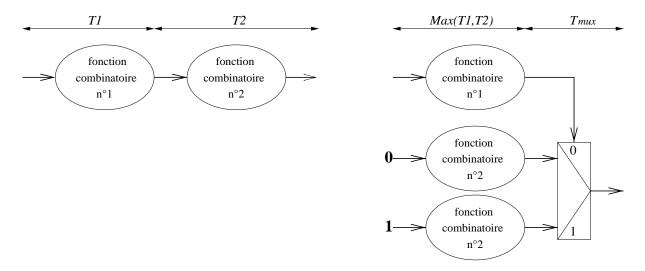

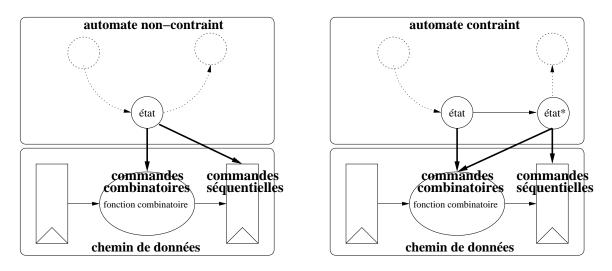

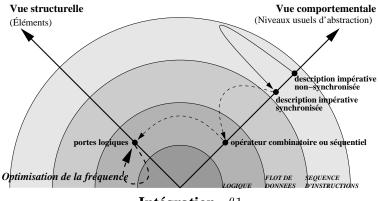

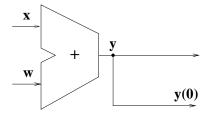

L'entrée de la synthèse de haut niveau est une description séquentielle non synchronisée représentant un coprocesseur. L'objectif final est d'obtenir la vue physique du circuit.

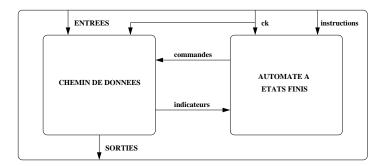

La synthèse est matérialisée dans la figure 2.2 par un arc (a) allant de la vue comportementale à la vue structurelle et de deux autres ((b) et (c)) retournant à la vue comportementale. Il symbolise la production d'une vue structurelle comprenant les descriptions comportementales synchronisées d'un chemin de données (DP) et d'un automate à états finis qui envoie des commandes vers le chemin de données (FSM).

#### Les applications visées

Le type d'application visé est une application dont le comportement est très dépendant des données (control dominated). Elle se caractérise par des traitements fonctionnels irréguliers comportant de nombreuses instructions de branchement avec des tests sur les données (un décodeur de Huffmann par exemple).

Elle diffère des applications pipelinées peu dépendantes des données qui ont un fonctionnement très régulier telle une DCT (Discret Cosinus Transform).

#### Les entrées et les sorties de la synthèse

Le niveau d'entrée que nous nous fixons est une description séquentielle non synchronisée décrivant le comportement d'un coprocesseur spécialisé.

L'entrée de la synthèse est écrite dans un langage impératif ne comportant aucune référence à une horloge. Le niveau de la sortie est une vue structurelle cadencée par une horloge comprenant un chemin de données ainsi qu'un automate de commandes.

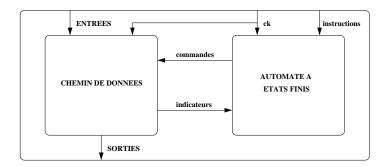

FIG. 2.3 Cible de la synthèse de haut niveau.

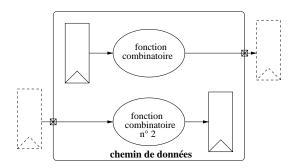

La figure 2.3 décrit de manière schématique la structure de la sortie de la synthèse. Le chemin de données est contrôlé par l'automate à états finis. Cet automate envoie des commandes sur le chemin de données reproduisant les opérations fonctionnelles décrites dans la spécification comportementale. Le chemin de données effectue l'ensemble des traitements sur les données.

Le chemin de données contient deux types d'opérateurs matériels :

- les opérateurs combinatoires (logiques ou arithmétiques).

- les composants séquentiels (éléments mémorisants de type registres, banc de registres, etc...).

#### Exploration de l'espace des solutions

Le concepteur a une vision globale du résultat qu'il veut obtenir. Son premier objectif est d'arriver à une réalisation matérielle dont les caractéristiques physiques tels que les temps de propagation, la surface, la puissance consommée, ne soient pas rédhibitoires pour le circuit.

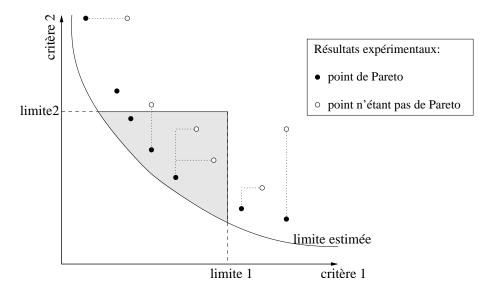

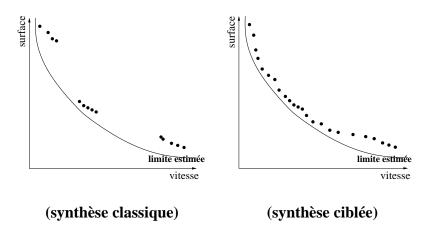

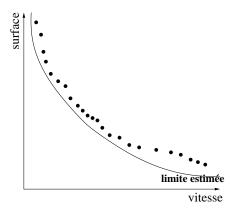

FIG. 2.4 Espace des solutions à deux dimensions.

La figure 2.4 représente un espace des solutions proposées par un outil par rapport à deux critères quelconques (par exemple : la surface et la puissance consommée). Un *point de Pareto* est un point pour lequel il n'existe aucune solution meilleure atteignable par l'outil sur les axes de l'espace des solutions [Mic94a]. La courbe de la *limite estimée* représente le résultat "idéal" estimé. Elle peut représenter, par exemple, une conception "à la main" par un concepteur expérimenté. Le concepteur pose des contraintes sur chaque axe pour délimiter l'espace des solutions acceptables (surface en grisé sur la figure 2.4).

Nous cherchons à mesurer la qualité de l'outil dans l'espace des solutions restreint (surface grisée) que cible le concepteur. La distance des *points de Pareto* à la courbe "idéale" nous informe sur l'efficacité de l'outil.

Cet espace ne se limite souvent pas à deux critères, explorer l'espace des solutions revient à considérer l'hyper-espace décrite par les *points de Pareto*. L'objectif de la synthèse de haut niveau est de pouvoir couvrir cet espace des solutions en obéissant aux directives du concepteur.

Comme pour une démarche "à la main", le concepteur doit pouvoir contrôler les critères d'optimisation de son circuit. De plus, l'outil a pour tâche de produire le résultat le plus efficace possible dans l'espace des solutions acceptables.

#### 2.2.2 Environnement du coprocesseur

Le coprocesseur synthétisé doit s'insérer dans un ensemble matériel déjà existant ou caractérisé. Il en résulte un certain nombre de contraintes à respecter par le coprocesseur synthétisé.

#### **Communications fonctionnelement asynchrones**

Pour la plupart des applications visées par les systèmes intégrés sur puce (télécommunication, automobile, vidéo), le comportement dynamique du système auquel appartient le coprocesseur est imprédictible. Tout au plus, le comportement du système peut imposer une borne maximale sur le nombre de cycles autorisés pour réaliser un traitement. Nous considérons donc que les communications avec l'environnement sont fonctionnelement asynchrones : cela signifie que les lectures et les écritures effectuées par le coprocesseur doivent être bloquantes.

**Remarque :** Un système fonctionnelement asynchrone peut être électriquement synchrone (les composants ont la même horloge). Ce sont les communications entre les différents composants du système qui sont asynchrones.

#### Fréquence d'horloge

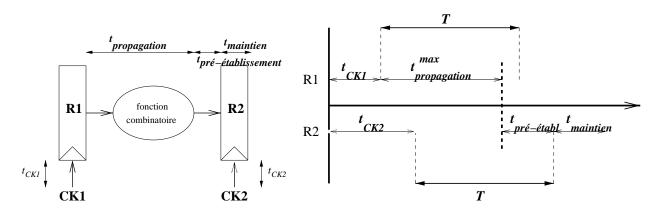

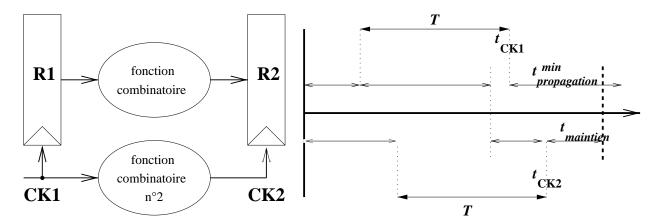

Le résultat de la synthèse est un circuit logique synchrone cadencé par une horloge.

La chaîne longue est le chemin fonctionnel entre deux registres où le temps de propagation est le plus long en tenant compte des temps de préétablissement et de maintien des registres. Par conséquent, la fréquence de fonctionnement est l'inverse du temps de propagation de la chaîne longue.

Le système dans lequel est plongé le coprocesseur impose son horloge au coprocesseur synthétisé. Le non-respect de cette fréquence de fonctionnement est rédhibitoire pour l'intégration de ce circuit. Du fait de l'importance de ce critère, l'outil *ugh* prend en compte la fréquence de l'horloge comme une contrainte d'entrée et non comme un résultat de la synthèse. Ainsi, les résultats produits à ce stade respecteront cette fréquence. Ce qui facilitera la continuité entre la synthèse de haut niveau et les autres outils de CAO de circuits pour produire la vue physique.

- L'entrée de la synthèse de haut niveau est une description comportementale séquentielle sans référence à une horloge.

- La fréquence est une entrée de la synthèse de haut niveau.

- Les communications externes du coprocesseur sont fonctionnelement asynchrones. C'est à dire que les lectures et écritures sont bloquantes.

- Les sorties de la synthèse de haut niveau constituent un ensemble couvrant le plus largement possible l'espace des solutions.

- Chaque solution est une description structurelle synchrone, c'est à dire cadencée par une unique horloge. Elle est composée d'un chemin de données et d'un automate d'états finis.

### 2.3 Les principes de la synthèse de haut niveau

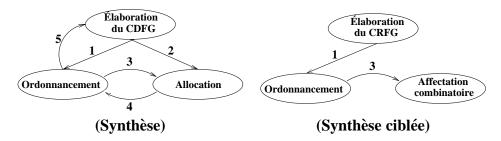

#### 2.3.1 Phases de la synthèse de haut niveau

Trois phases composent la synthèse de haut niveau. Il s'agit de l'élaboration du graphe de flot de données et de contrôle, de l'allocation de ressources et de l'ordonnancement temporel au niveau

cycle.

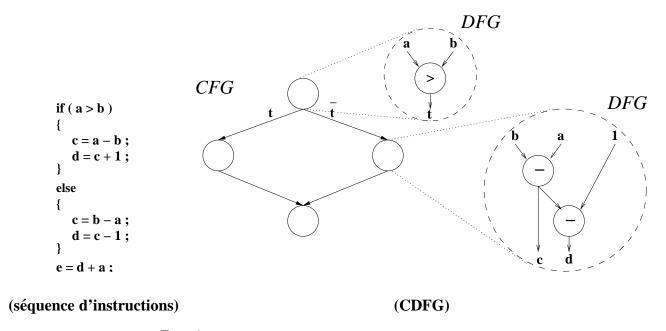

#### Élaboration du graphe de flot de données et de contrôle

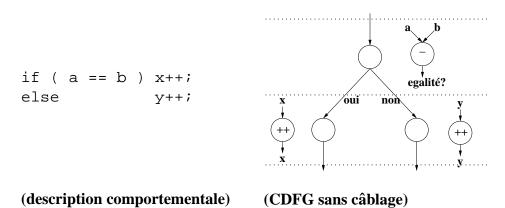

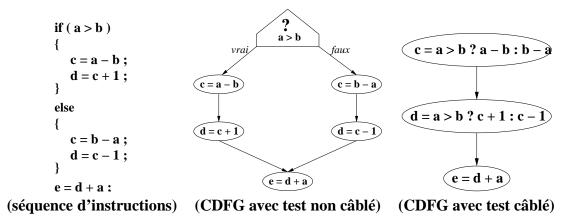

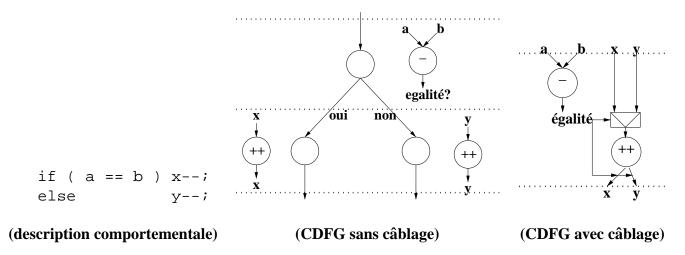

Le but de cette phase est de construire le squelette de l'automate à états finis qui contrôle le coprocesseur et, en particulier, d'identifier les branchements conditionnels qui seront présents dans l'automate.

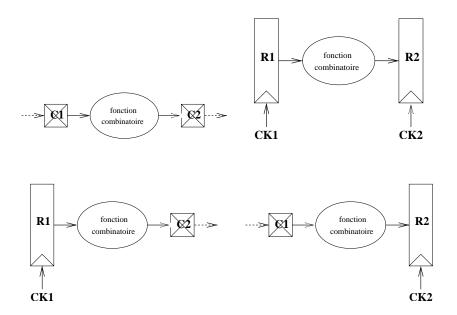

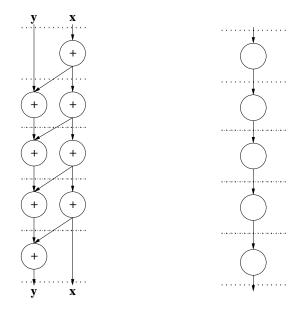

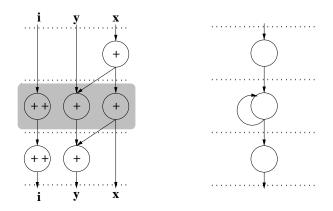

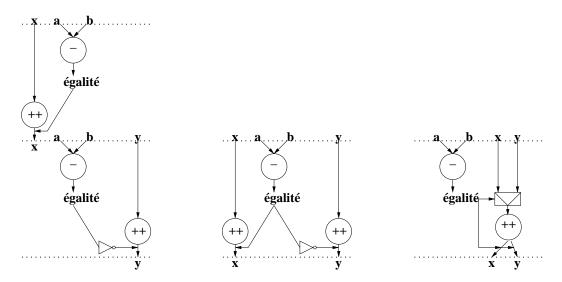

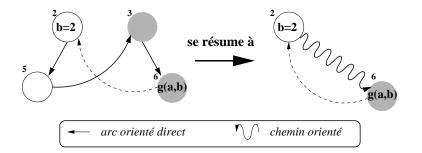

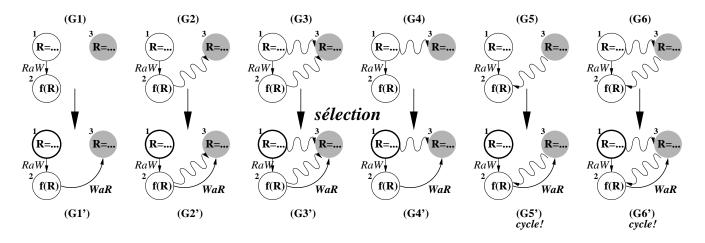

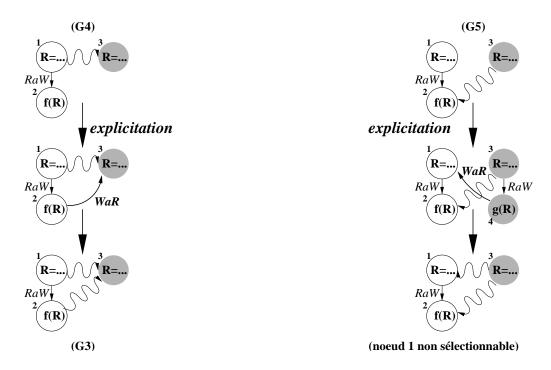

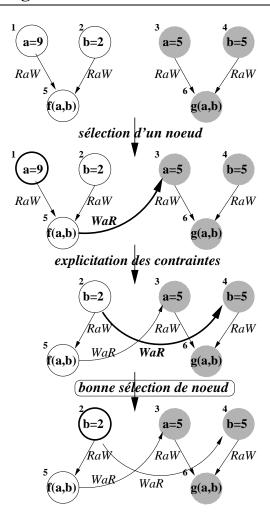

Le graphe de flot de données et de contrôle (CDFG) est la fusion du graphe de flot de données (DFG) et du graphe de flot de contrôle (CFG). Dans le CFG, les séquences d'opérations sans branchement sont représentées par des noeuds et les branchements entre deux séquences (boucles, sauts conditionnels) par des arcs. Le DFG représente les dépendances de données à l'intérieur d'un bloc d'opérations séquentielles.

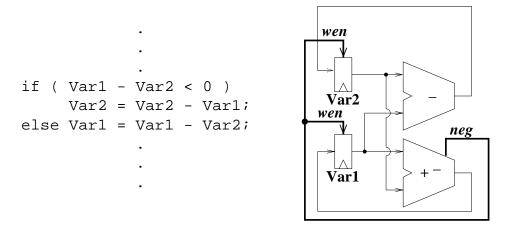

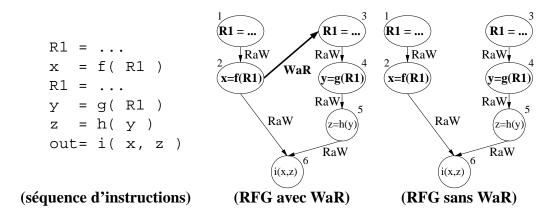

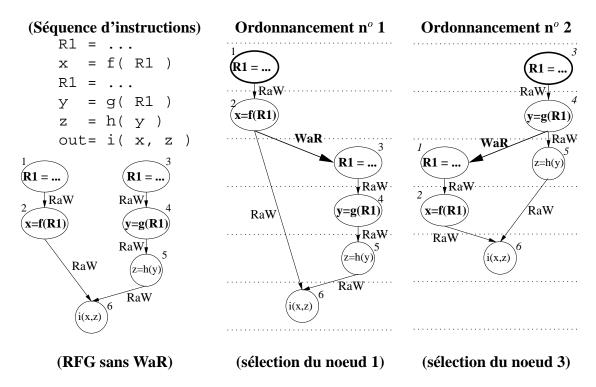

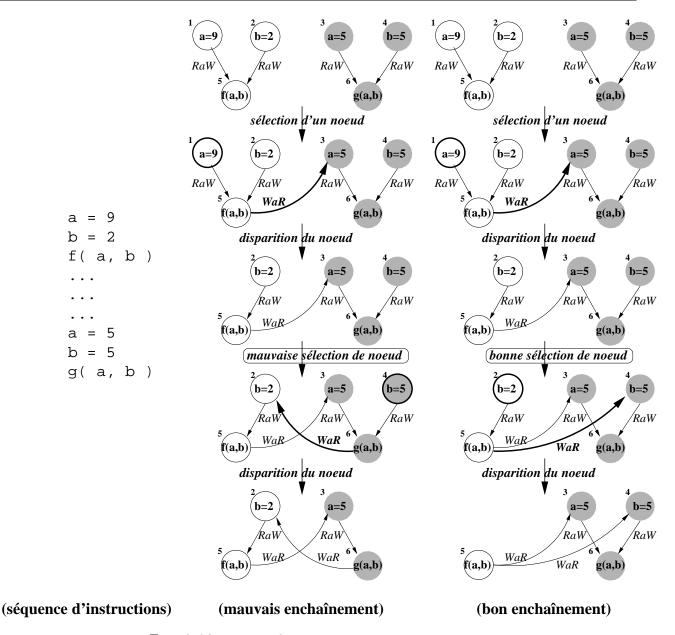

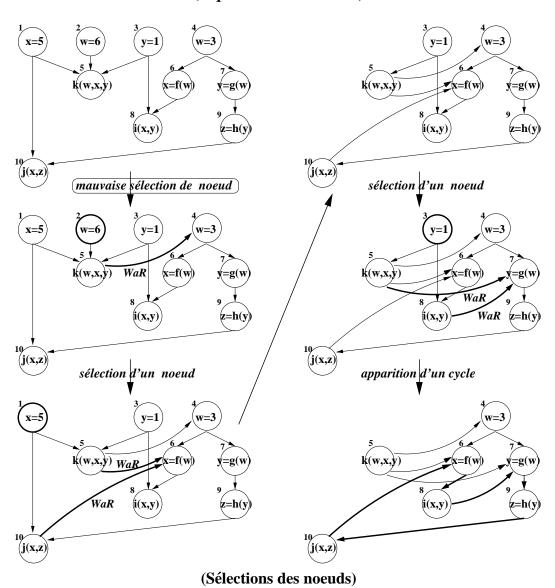

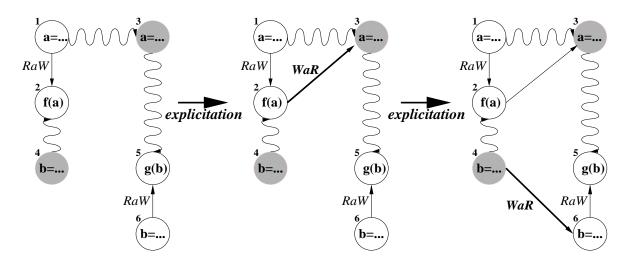

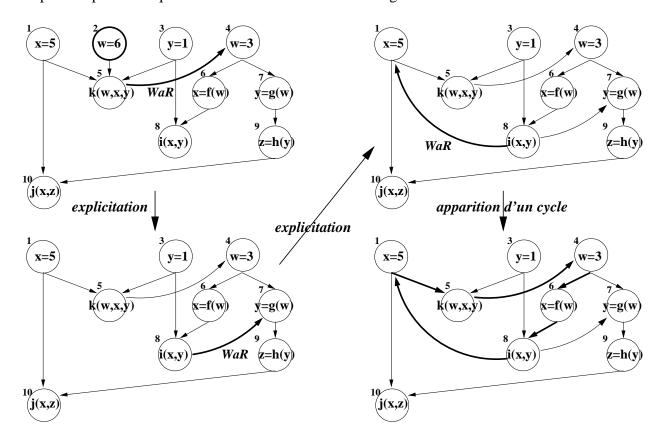

Le CDFG représente les dépendances entre toutes les opérations fonctionnelles de la description comportementale. Dans ce graphe, chaque noeud est une opération séquentielle et chaque arc symbolise une contrainte de précédence dans l'ordonnancement des opérations fonctionnelles. Les contraintes de précédence matérialisent l'impossibilité de faire une action avant une autre pour garder la cohérence globale du comportement initial. La figure 2.5 donne une représentation graphique d'un CDFG.

FIG. 2.5 Un CDFG d'une séquence d'instructions.

La phase d'élaboration du CDFG cherche à optimiser la topologie de l'automate en vue de l'ordonnancement et de l'allocation. En effet, le CDFG peut être optimisé pour minimiser le nombre de cycles ou la surface occupée par le coprocesseur. Certains DFG composant le CDFG peuvent être regroupés en un seul DFG.

Les changements de topologie du CDFG peuvent être des déroulements de boucles, des branchement câblés dans le chemin de données, etc... Deux DFG séparés par un branchement (dans l'exemple de la figure 2.5, il s'agit des deux noeuds du CDFG séparés par les conditions t et  $\overline{t}$ ) peuvent être réunis pour former un branchement câblé.

Le regroupement des DFG supprime les branchements dans l'automate à états finis. L'ordonnancement est plus efficace sur un gros DFG que sur plusieurs petits DFG. Le regroupement des DFG optimise donc le nombre de cycles.

D'un autre côté, le regroupement de DFG transfère le test de branchement dans le chemin de données et augmente la complexité de la partie opérative. Le regroupement des DFG augmente donc la surface du coprocesseur.

#### L'ordonnancement

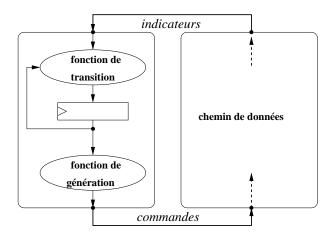

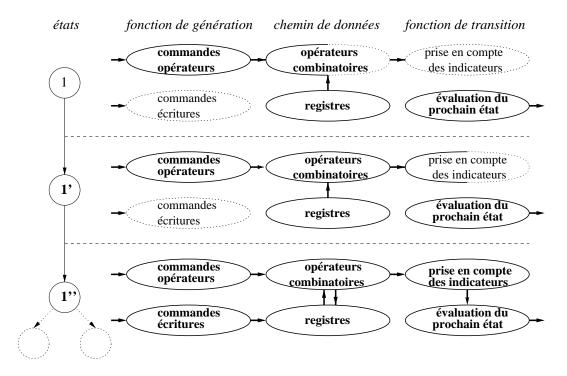

Le but de l'ordonnancement est de construire la *fonction de transition* de l'automate à états finis constituant la partie contrôle du coprocesseur.

L'ordonnancement ne remet pas en cause les branchements présents dans le CDFG. Chaque DFG du CDFG est ordonnancé séparément.

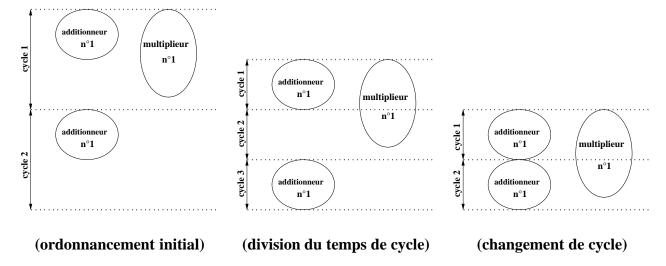

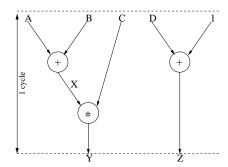

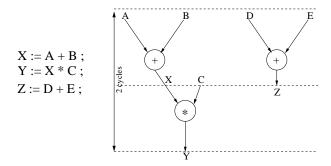

A partir des temps de propagation des opérateurs matériels, l'ordonnancement détermine les frontières temporelles des cycles sur les opérations fonctionnelles du DFG [Mic94b]. Chaque cycle nécessite des opérateurs matériels pour réaliser les opérations fonctionnelles de la description comportementale. Plusieurs opérations fonctionnelles peuvent être parallélisées dans un même cycle.

**Remarque :** Le nombre minimal d'opérateurs matériels (combinatoires et séquentiels) nécessaires pour faire le chemin de données est connue à la fin de la phase d'ordonnancement.

#### Allocation matérielle

Le but de l'allocation est la définition de la structure du chemin de données du coprocesseur.

L'allocation sert à déterminer le nombre d'opérateurs matériels nécessaires ainsi que leurs types et la façon dont ils sont interconnectés. L'allocation peut soit ajouter un opérateur, soit partager un opérateur déjà existant en liant cet opérateur à plusieurs opérations fonctionnelles de la description comportementale [GDWL92].

- allocation et affectation des registres : détermination du nombre de registres. Les registres sont liés aux variables de la description comportementale pour stocker les données à chaque cycle. On décide à ce stade, si les variables correspondent à des registres ou à de simples signaux combinatoires.

- 2. allocation et affectation des opérateurs combinatoires : détermination du nombre d'opérateurs combinatoires. A chaque cycle, on connaît la liste des opérations fonctionnelles à exécuter. Pour cela, des opérateurs combinatoires sont sélectionnés et attachés à ces opérations fonctionnelles.

- 3. mise en place de la connectique (bus et multiplexeurs).

Chaque opérateur occupe de la surface et cela a un coût lors de la production en série. L'allocation cherche à diminuer la surface occupée par le coprocesseur. Pour ce faire, elle doit optimiser l'utilisation des opérateurs en les partageant entre différentes opérations fonctionnelles.

**Remarque :** Multiplexer une entrée d'opérateur pour le partager revient à ajouter de la logique combinatoire au circuit. Cela réduit le gain de surface engendré par le partage de cet opérateur.

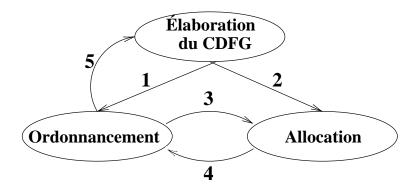

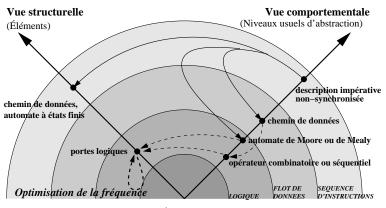

#### 2.3.2 Cercles vicieux de la synthèse

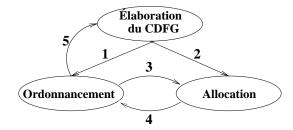

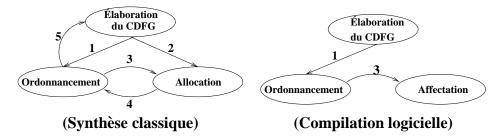

FIG. 2.6 Cercles vicieux de la synthèse de haut niveau.

Les optimisations effectuées dans les trois étapes de la synthèse de haut niveau sont très liées et les décisions ne peuvent être prises indépendamment dans chaque phase sans risquer de compromettre la qualité du résultat.

La figure 2.6 représente les dépendances entre les phases :

- Arc 1 L'ordonnancement se base sur les DFG extraits du CDFG.

- **Arc 2** Le CDFG influence le nombre minimal d'opérateurs en nécessitant des opérateurs pour les branchements câblés.

- **Arc 3** L'allocation se base sur la parallélisation des opérations fonctionnelles pour déterminer le nombre de ressources matérielles nécessaires.

- Arc 4 Dans la phase d'allocation et d'affectation, le partage d'un opérateur entre deux opérations fonctionnelles implique le plus souvent l'ajout de combinatoire sur ses entrées (multiplexage).

Le partage d'un opérateur augmente le temps de propagation de ce dernier.

La phase d'allocation influence donc l'ordonnancement car il modifie l'évaluation temporelle

- La phase d'allocation influence donc l'ordonnancement car il modifie l'évaluation temporelle sur laquelle se base l'ordonnancement.

- **Arc 5** La détermination des blocs d'instructions séquentielles dans le CDFG se fait indépendamment des contraintes temporelles des opérateurs matériels. Un mauvais ordonnancement peut alors empêcher une parallélisation efficace des opérations fonctionnelles.

L'ordonnancement doit pouvoir remettre en cause la phase d'élaboration du CDFG.

La synthèse peut toujours produire une solution de base par une démarche linéaire : construction du CDFG, ordonnancement puis allocation. Mais celle-ci est souvent inutilisable du fait des piètres caractéristiques du résultat.

Les arcs 4 et 5 de la figure 2.6 sont des phases d'optimisations des caractéristiques du circuit. Ce sont elles qui constituent les cercles vicieux.

C'est l'existence de cycles dans le graphe de la figure 2.6 qui constitue la principale difficulté de la synthèse de haut niveau.

Du fait de la complexité des algorithmes, les outils de synthèse de haut niveau sont très lents. Le travail d'exploration architecturale en est rendu plus difficile pour le concepteur.

#### Échapper aux cercles vicieux

Deux approches sont possibles pour traiter les dépendances croisées :

⇒ une automatisation totale de la synthèse où on itère les différentes phases de la synthèse jusqu'à obtenir une solution satisfaisante. Elle peut éventuellement impliquer des heuristiques pour converger plus rapidement vers une solution.

⇒ des informations supplémentaires fournies par l'utilisateur pour casser les cycles de dépendance et réduire le nombre de choix.

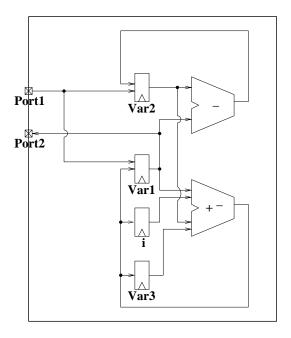

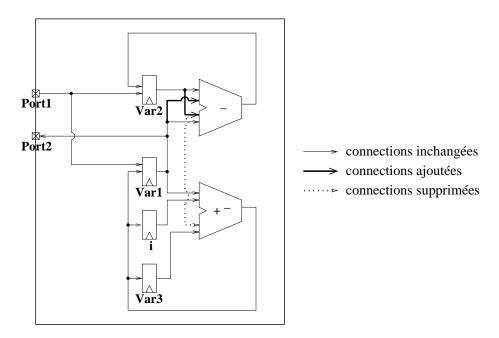

L'outil de synthèse de haut niveau *ugh* s'appuie sur un ajout d'informations de la part de l'utilisateur. Le concepteur doit définir le nombre d'éléments mémorisants. Chaque registre est identifié dans la description comportementale. La synthèse ne pourra pas ajouter d'autres registres pour construire l'architecture cible. D'emblée, l'affectation des registres de la phase d'allocation (cf. chapitre 2.3.1) est résolue.

#### 2.3.3 Multiplicité et antagonisme des objectifs

L'évaluation d'une solution est assez complexe car elle est multi-critères. Le concepteur s'attache surtout aux caractéristiques suivantes de son circuit :

- la fréquence d'horloge.

- le temps d'exécution global.

- la surface.

- la consommation.

Dès que l'on cherche à optimiser la surface, les temps de propagation ou la vitesse du coprocesseur, la synthèse de haut niveau se heurte à l'antagonisme de ces critères. L'optimisation d'un critère particulier peut avoir des répercussions néfastes sur les autres.

L'antagonisme des critères augmente la complexité de la synthèse de haut niveau. L'élaboration du CDFG peut, par exemple, choisir d'optimiser la surface ou bien le temps d'exécution global.

#### Échapper à la multiplicité des objectifs

Pour simplifier la synthèse, nous décidons de réduire le nombre de critères caractérisant la solution pour avoir un objectif plus simple.

Le changement de fréquence, de surface et de temps d'exécution influence la consommation. Si l'utilisateur vise un coprocesseur à faible consommation, il devra, soit réduire la fréquence de fonctionnement, soit cibler une surface plus réduite. Nous faisons l'hypothèse que le changement de la fréquence ou de la surface permet de contrôler la consommation. La consommation n'est plus un objectif de la synthèse mais devient une conséquence des choix d'optimisation des autres critères.

La fréquence d'horloge étant une contrainte d'entrée de notre outil de synthèse de haut niveau, il reste deux degrés de liberté qui sont la surface de silicium et le temps d'exécution (en nombre de cycles).

- L'outil de synthèse haut niveau doit être suffisamment rapide pour permettre l'exploration architecturale.

- Pour réduire la complexité de la synthèse de haut niveau, nous faisons le postulat que l'affectation des registres est faite. Les registres sont identifiés et liés aux opérations fonctionnelles de la description comportementale.

- Nous supposons que la consommation est gouvernée par la fréquence et la surface. La consommation ne fait pas partie des objectifs directs de la synthèse.

- L'espace des solutions se réduit aux critères suivants :

- le temps d'exécution global.

- la surface.

### 2.4 Les problèmes ouverts

#### 2.4.1 Comment restreindre l'espace des solutions?

Nous avons vu dans le chapitre 2.2.2 que la fréquence d'horloge est une contrainte d'entrée pour la synthèse de haut niveau. Dans le chapitre 2.3.2, nous décidons aussi pour des raisons algorithmiques de définir explicitement les registres. D'autres informations sont-elles nécessaires pour ne pas trop s'écarter d'une conception "à la main" idéale, tout en permettant une exploration efficace de l'espace des solutions ?

La description comportementale et la fréquence ne sont pas des entrées suffisantes pour circonscrire le domaine des solutions. Il doit y avoir directives supplémentaires pour mieux correspondre aux objectifs que s'est fixé le concepteur. A savoir :

- le temps d'exécution global.

- la surface.

Comment cibler un intervalle dans cet espace?

Le concepteur peut fournir à l'outil de haut niveau plus de contraintes sur la surface du circuit ou sur sa vitesse.

Par exemple, en plus du nombre de registres, le concepteur peut fournir l'affectation de ces registres. Il peut aussi fournir des informations sur la taille en nombre de bits des opérateurs du chemin de données. Cela permet de cibler plus précisément la surface du circuit à synthétiser.

Les informations supplémentaires données à l'outil pour cibler précisément une solution coûte du temps au concepteur. Il faut veiller à ce que ce coût soit le plus faible possible.

Quelles sont les informations indispensables à la réduction de l'espace des solutions ?

- ✓ Comment réduire le champ des solutions que donne la synthèse de haut niveau ?

- ✓ Quelles informations supplémentaires faut-il ajouter à la description pour qu'elle soit synthétisable dans l'espace des solutions visées ?

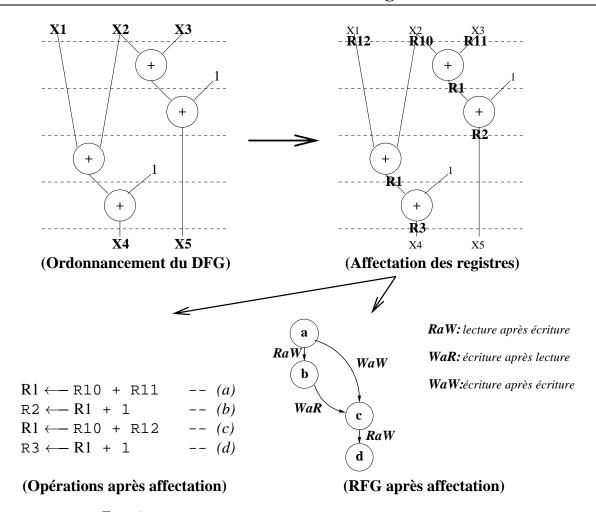

# 2.4.2 Qu'apporte la connaissance des registres sur l'algorithme de la synthèse?

Nous avons vu que pour restreindre l'espace des solutions, nous pouvions fournir l'affectation des registres à l'outil de synthèse de haut niveau. Quelles en sont les implications dans l'algorithme de la synthèse de haut niveau?

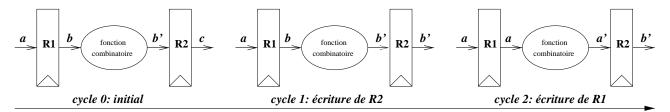

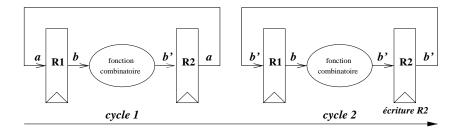

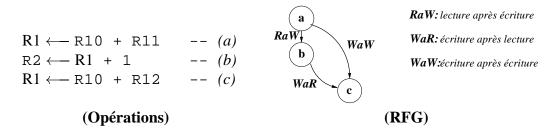

Pour éviter le cercle vicieux de la synthèse et produire un résultat rapidement, le chapitre 2.3.2 pose une hypothèse forte : les registres sont connus. Le fait que la synthèse haut niveau connaisse une partie de l'architecture cible nous ramène à un problème de compilation logicielle.

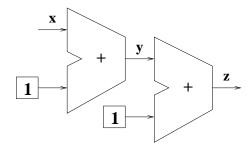

$$\mathbf{R1} \leftarrow \mathbb{R}10 + \mathbb{R}11 \qquad -- \quad (a)$$

$\mathbb{R}2 \leftarrow \mathbf{R1} + 1 \qquad -- \quad (b)$

$\mathbf{R1} \leftarrow \mathbb{R}10 + \mathbb{R}12 \qquad -- \quad (c)$

$\mathbb{R}3 \leftarrow \mathbf{R1} + 1 \qquad -- \quad (d)$

FIG. 2.7 Partage du registre R1.

En compilation, le partage d'éléments mémorisants illustré par la figure 2.7 entraîne des contraintes sur l'utilisation de ces registres. Les différents accès au registre RI en lecture ou en écriture ne peuvent être ordonnancés de n'importe quelle façon. Pour garder la cohérence de la description initiale, on ne peut, par exemple, intervertir l'instruction (b) et l'instruction (c). La valeur contenue dans RI serait alors remplacée avant d'avoir pu être lue.

Ces contraintes d'ordonnancement ne sont pas évoquées dans la synthèse de haut niveau classique car les registres ne sont pas identifiés dans la description comportementale.

Dans notre synthèse ciblée de haut niveau, les registres sont déjà affectés. Le partage éventuel de ces registres nous amène à considérer les mêmes contraintes sur l'ordonnancement que pour la compilation logicielle. La construction du CDFG doit respecter les contraintes de précédence issues du partage des registres.

La connaissance des registres a aussi des répercussions sur l'algorithme d'ordonnancement et d'allocation. Dans le chapitre 2.4.1, nous nous demandons s'il faut ajouter des informations pour mieux cibler la solution. Est-ce que ces informations simplifieront la complexité de l'algorithme ?

- ✓ Est-ce que l'affectation des registres résout tous les cercles vicieux de la synthèse ?

- ✓ Quelles sont les contraintes issues de la compilation logicielle dont la synthèse hérite ?

- ✓ Est-ce que l'affectation des registres est suffisante pour produire un algorithme simple et efficace ?

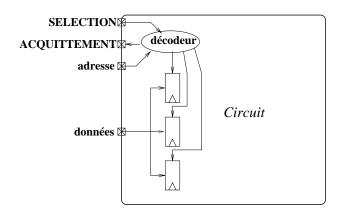

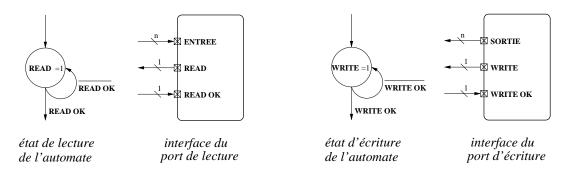

#### 2.4.3 Quelle formes ont les communications externes?

Dans le chapitre 2.2.2, nous constatons que les communications du coprocesseur sont fonctionnelement asynchrones avec l'environnement. Les accès aux ports d'entrées/sorties doivent être encapsulés par des opérations de synchronisation. Pour garantir la compatibilité avec l'environnement, le protocole de communication doit être suffisamment répandu ou assez simple pour être adapté via une interface. Doit-on laisser le choix du mode d'accès à l'utilisateur?

- ✓ Quel protocole de communication respectant les contraintes de l'asynchronisme choisir ?

- ✓ Devons-nous laisser leur description à la charge de l'utilisateur ?

#### 2.4.4 Comment prendre en compte les caractéristiques électriques du circuit ?

L'un des objectifs de la synthèse de haut niveau est de prendre en compte les caractéristiques électriques de la bibliothèque de cellules cibles.

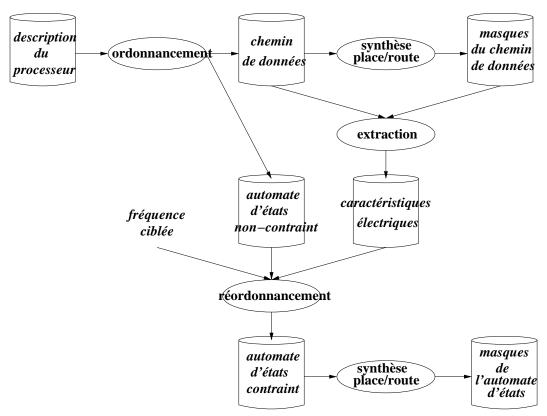

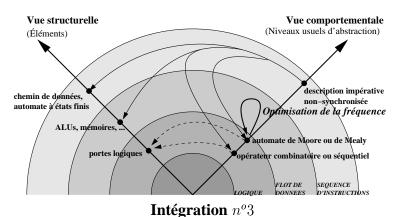

FIG. 2.8 Dépendance de la synthèse par rapport aux caractéristiques physiques

Les contraintes électriques sont obtenues une fois le circuit placé et routé. Elles sont constituées des temps de propagation des opérateurs combinatoires et des temps de préétablissement et de maintien des registres et des bancs mémoire.

Pour respecter la fréquence d'horloge, l'outil de synthèse de haut niveau doit adapter son ordonnancement en fonction des caractéristiques temporelles des opérateurs du chemin de données. Or ces caractéristiques physiques ne sont connues qu'une fois obtenue la vue physique du coprocesseur (figure 2.8). Il y a donc une dépendance mutuelle entre la phase de synthèse et la phase placement/routage.

- ✓ Existe-t-il une méthode efficace qui permette de tenir compte des contraintes électriques pour la synthèse de haut niveau?

- ✓ Comment adapter l'ordonnancement à cette méthode ?

# 2.4.5 Comment interfacer l'outil de synthèse haut niveau avec les outils de synthèse RTL?

Dans le domaine de la CAO de circuit, il existe de nombreux outils de synthèse performants au niveau RTL (Register Transfer Level). L'objectif de la synthèse de haut niveau n'est pas de les réinventer mais d'être inter-opérable avec eux.

Le résultat de la synthèse de haut niveau est une description synchrone de niveau RTL.

D'autres outils de CAO de circuit sont censés prendre en entrée les résultats de la synthèse haut niveau et il est inutile de prendre des décisions qui seront remises en cause par ces outils. Où doit s'arrêter la synthèse de haut niveau pour laisser la place à des outils de synthèse spécialisés ?

Les outils de synthèse de bas niveau sont avantagés par rapport aux outils de synthèse de haut niveau. Par exemple, la phase de projection structurelle de la synthèse logique connaît les caractéristiques électriques intrinsèques des cellules qu'elle utilise pour réaliser les fonctions booléennes. Ses algorithmes sont ciblés pour cette utilisation et sont très efficaces.

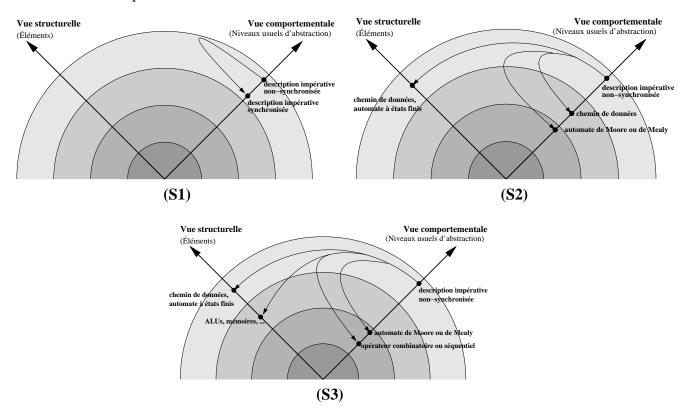

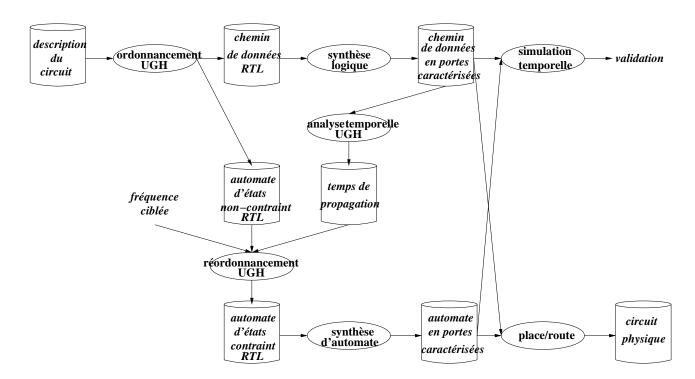

FIG. 2.9 Trois niveaux de sortie pour la synthèse de haut niveau.

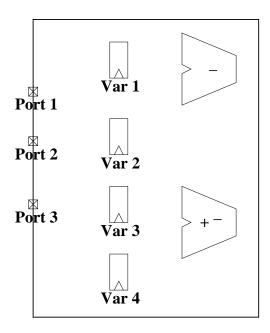

Nous considérerons donc plusieurs niveaux de sorties possibles décrites dans la figure 2.9 :

- ⇒ La sortie *S1* est une description comportementale de niveau RTL où la partie opérative n'est pas dissociée de l'automate d'états. La synthèse de haut niveau n'a déterminé que les *fonctions* de transition et de génération de l'automate d'états. L'allocation des ressources est laissée aux autres outils de synthèse.

- ⇒ La sortie S2 est une vue structurelle constituée de deux descriptions comportementales de niveau RTL (DP et FSM). La partie opérative est donc séparée de l'automate. L'allocation des ressources est laissée aux autres outils de synthèse.

- ⇒ La sortie S3 est une vue structurelle constituée d'un DP et d'un FSM tous deux de niveau RTL. L'automate est une description comportementale et le chemin de données une vue structurelle composée d'instances d'opérateurs. L'allocation des ressources est faite par la synthèse de haut niveau.

2.5 Conclusion 31

La synthèse haut niveau ne produit pas de vue structurelle de l'automate. C'est une tâche inutile puisque la synthèse d'automate produit un résultat largement satisfaisant.

La différence entre S1 et S2 est la séparation du chemin de données de l'automate d'états. La sortie S1 fusionne les deux comportements pour donner une description synchronisée du coprocesseur. S1 et S2 de la figure 2.9 ne font pas d'allocation du chemin de données alors que S3 va jusqu'à l'affectation des opérateurs (cf. chapitre 2.3.1).

Suivant le type de sortie, le flot de conception et le résultat final ne seront pas les mêmes. Nous avons vu dans le chapitre 2.4.4 qu'il faut faire intervenir les contraintes électriques lors de la synthèse. La forme de la sortie influence-t-elle sur la manière de faire intervenir ces contraintes ?

- ✓ Quel est le niveau de description de la sortie de la synthèse de haut niveau le plus adapté aux autres outils de CAO?

- ✓ Est-ce que le choix d'un niveau de sortie à des répercussions sur les possibilités de faire intervenir les contraintes électriques ?

#### 2.5 Conclusion

Notre outil de synthèse de haut niveau prend en entrée :

- la description comportementale non synchronisée d'un coprocesseur.

- la fréquence du coprocesseur.

- les registres du coprocesseur.

Notre outil de synthèse de haut niveau génère en sortie :

un coprocesseur avec des communications fonctionnelement asynchrones. Il est caractérisé par sa surface et son temps d'exécution global.

L'objectif de cette thèse est de répondre aux problèmes que posent ces conditions :

- ✓ Comment réduire le champ d'investigation de la synthèse de haut niveau ? Quelles sont les caractéristiques d'un langage synthétisable ? Comment prendre en compte les desiderata du concepteur ?

- ✓ Comment modéliser les communications asynchrones du coprocesseur ?

- ✓ Quelles sont les contraintes de réordonnancement des accès aux registres ? Est-ce que des informations supplémentaires peuvent simplifier les algorithmes de la synthèse haut niveau ?

- ✓ Comment tenir compte des caractéristiques électriques ?

- ✓ Comment insérer la synthèse de haut niveau dans le flot de conception ? Peut-on toujours tenir compte des contraintes électriques ?

Problématique Problématique

# Chapitre 3

# État de l'art

## Sommaire

| 3.1 | Les algorithmes d'ordonnancement                |  |

|-----|-------------------------------------------------|--|

|     | ASAP et ALAP                                    |  |

|     | Ordonnancement par liste de priorité            |  |

|     | Ordonnancement basé sur les distributions       |  |

|     | Ordonnancement basé sur les chemins d'exécution |  |

| 3.2 | Les algorithmes d'affectation                   |  |

|     | 3.2.1 Affectation des opérateurs combinatoires  |  |

|     | Partitionnement en cliques                      |  |

|     | 3.2.2 Affectation des registres                 |  |

|     | Left edge                                       |  |

|     | Comparaison bipartite par poids                 |  |

| 3.3 | Les outils de synthèse haut niveau              |  |

|     | 3.3.1 Outils orientés flot de données           |  |

|     | GAUT                                            |  |

|     | cathedral 2/3                                   |  |

|     | 3.3.2 Outils mixtes                             |  |

|     | amical                                          |  |

|     | camad                                           |  |

|     | behavioral compiler et CoCentric                |  |

|     | music                                           |  |

| 3.4 | Conclusion                                      |  |

|     |                                                 |  |

34 État de l'art

epuis les années 1970, des outils de synthèse de haut niveau ont été développés aussi bien dans les milieux académiques qu'industriels. Nous présentons dans ce chapitre les différentes approches existantes et les techniques sur lesquelles elles s'appuient.

En effet, un outil de synthèse est avant tout un algorithme. Son type est déterminant dans l'efficacité du traitement. Pour simplifier la complexité du problème, il est la plupart du temps scindé en deux parties : une partie pour extraire l'ordonnancement des opérations fonctionnelles, une autre pour déterminer les opérateurs matériels nécessaires à ces opérations.

La description des méthodes générales utilisées pour ces deux aspects de la synthèse de haut niveau correspondent respectivement aux deux premiers sous-chapitres.

Nous verrons ensuite leur mise en application dans les outils de synthèse et l'interaction que ces derniers ont avec le concepteur.

### 3.1 Les algorithmes d'ordonnancement

L'objectif de l'ordonnancement est de déterminer à quel cycle s'effectue les opérations fonctionnelles contenues dans la description comportementale du circuit. Il détermine donc le parallélisme des opérations et influence fortement la surface du circuit.

Ils existent quatre familles d'algorithmes d'ordonnancement :

- 1. algorithmes de programmation linéaire en nombre entiers : reformulent le problème d'ordonnancement comme un problème de programmation linéaire au moyen d'inéquations dues aux contraintes. Ils fournissent une solution optimale [CWM94].

- 2. *algorithmes neuronaux* : modélisent le problème d'ordonnancement par un réseau de neurones trouvant une solution par auto-réorganisation [Phi92].

- 3. *les algorithmes itératifs/constructifs* : répartissent les opérations dans le temps les unes après les autres suivant un critère de priorité sur chacune d'elles.

Pour la synthèse de haut niveau, le nombre d'opérations à ordonnancer est très important, les outils de synthèse ont besoin d'algorithmes rapides. Les *algorithmes de programmation linéaire en nombre entier* et les *algorithmes neuronaux* sont inadaptés à notre problème car ils entraînent des modèles mathématiques très complexes.

Les algorithmes que nous développons dans ce chapitre sont itératifs.

Certains algorithmes se limitent à l'ordonnancement d'un flot de données, d'autres sont plus orientés flot de contrôle. Cependant, ils obéissent tous au mêmes types de contraintes. [WC95] nous présente les différents types de contraintes sur l'ordonnancement :

- non contraint : seules les contraintes de précédence sur les données ordonnent les opérations.

- sous contrainte temporelle : l'ordonnancement doit obéir aux contraintes de précédence et le temps d'exécution de la tâche ne doit pas dépasser la limite temporelle.

- sous contrainte de ressource : l'ordonnancement doit obéir aux contraintes de précédence et ne pas dépasser un nombre maximum d'instanciations pour chaque type d'opérateur matériel.

• sous contrainte temporelle et de ressource : l'ordonnancement doit obéir aux contraintes de précédence, ne pas dépasser la limite temporelle et le nombre maximum d'instanciations d'opérateurs matériels.

Tous les types d'algorithmes d'ordonnancement respectent les contraintes de précédence afin de respecter la fonctionnalité des opérations.

#### **ASAP et ALAP**

Ils s'appliquent à des graphes de flots de données.

ASAP (As Soon As Possible) est un ordonnancement des opérations au cycle le plus tôt en ne tenant compte que des contraintes de précédence.

ALAP (As Late As Possible) est un ordonnancement des opérations au cycle le plus tardif sans que cela change le nombre total de cycles par rapport à un ordonnancement ASAP.

Ces algorithmes sont très rapides. Ils donnent un ordonnancement optimal en nombre de cycles mais coûtent cher en surface.

La mobilité d'une opération est égale à  $cycle_{ALAP} - cycle_{ASAP}$ , où  $cycle_{ALAP}$  et  $cycle_{ASAP}$  sont les cycles d'ordonnancement de l'opération, pour respectivement, un algorithme ALAP et un algorithme ASAP.

#### Ordonnancement par liste de priorité

L'ordonnancement par liste, ou *list scheduling*, cherche à minimiser le nombre de cycles. Cet algorithme prend en compte une contrainte sur les ressources.

Dans une suite d'opérations fonctionnelles sans branchement conditionnel, l'algorithme choisit à chaque cycle l'opération la plus prioritaire (tout en respectant les contraintes de précédence) [PG87]. La priorité des opérations peut être évaluée une fois pour toute au début de l'ordonnancement ou réévaluée à chaque cycle.

En général, les priorités utilisées sont la mobilité ou le nombre de successeurs de l'opération.

#### Ordonnancement basé sur les distributions

Cet algorithme aussi appelé *force directed scheduling*, cherche à minimiser le nombre de ressources. Il peut prendre une contrainte temporelle pour forcer la parallélisation des opérations.

Le principe de l'algorithme est de reporter les opérations les plus mobiles à des cycles nécessitant moins de ressources [PK89].

L'opération fonctionnelle est placée sur le cycle qui minimise le nombre total d'opérateurs.

L'estimation du nombre d'opérateurs est basée sur la mobilité des opérations.

La probabilité d'exécution d'une opération logicielle dans un cycle donné est l'inverse de sa mobilité. Le nombre d'opérateurs matériels est estimé pour chaque type d'opérateur et pour chaque cycle. Pour chaque type d'opérateur matériel, on ne considère que les opérations logicielles pouvant y être affectées.

36 État de l'art

Le nombre d'opérateurs nécessaires pour un cycle donné est la somme des probabilités d'exécution de chaque opération dans ce cycle.

Le nombre global d'opérateurs est le nombre qui satisfait la contrainte estimée pour chaque cycle.

Cet algorithme est plus lent car sa fonction de coût est complexe. Il reste un bon compromis entre le degré d'optimisation de la surface et le temps de calcul.

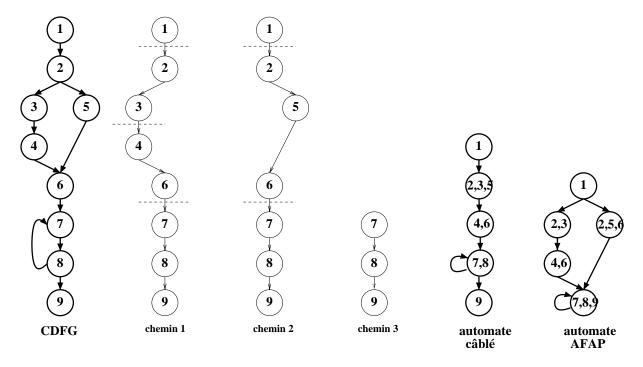

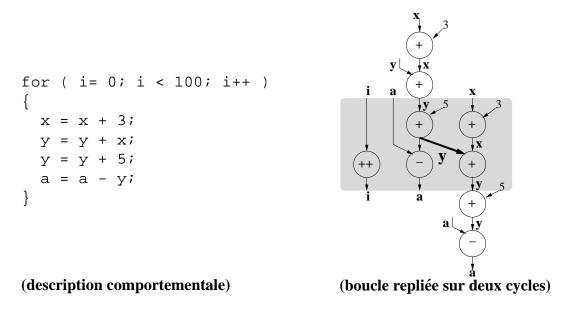

#### Ordonnancement basé sur les chemins d'exécution

Ce type d'algorithme est aussi appelé path-based scheduling [Cam91].

Au lieu de considérer une partie de la description, ces algorithmes considèrent l'intégralité du flot de description au moyen de CDFG (graphe mélangeant les flots de données au flot de contrôle).

Le flot de description est alors considéré dans son intégralité.

L'algorithme considère pour cela tous les chemins d'exécution.

Toutes les boucles dans le flot de contrôle sont cassées de manière à obtenir un graphe de contrôle sans cycle. On extrait les différents chemins d'exécution de ce graphe.

Le noeud initial de la description est le départ d'un chemin. Chaque boucle est aussi le départ d'un chemin car il peut y avoir plusieurs itérations sur la boucle. Donc s'il y a n boucles, il y a n+1 départs de chemin.

Chaque branchement conditionnel donne deux chemins différents. Par exemple dans la figure 3.1, il y a un chemin passant par les *noeuds 3 et 4* et un chemin passant par le *noeud 5*.

FIG. 3.1 Extraction des chemins du CDFG.

Pour chaque chemin d'exécution, on détermine les groupes d'opérations logicielles pouvant s'effectuer dans le même cycle. Les coupures sont placées en parcourant le chemin séquentiellement.

Un groupe courant est créé. Pour chaque opération du parcours :

- si l'opération n'est pas en conflit avec les autres opérations du groupe courant, on l'ajoute au groupe courant.

- sinon on l'ajoute à un nouveau groupe qui devient le groupe courant.

Ainsi une opération logicielle ne peut être associée qu'à l'opération suivante ou à l'opération précédente.

Les conflits sont déterminés à partir de contraintes de ressources (nombre d'opérateurs combinatoires ou conflit d'écriture sur les registres par exemple).

Tous les chemins sont ensuite réunis pour constituer l'automate d'états.

L'exécution d'opérations n'appartenant pas au même branchement sont mises sous des conditions d'exclusivité (câblage) pour être ordonnancées dans le même cycle. Les opérations intégrées dans une boucle sont dépendantes du test de fin de boucle.

Chaque coupure de chemin est répercutée dans l'automate d'états.

L'AFAP (As Fast As Possible) est un algorithme basé sur les chemins d'exécution qui produit l'automate le plus rapide en temps d'exécution. Mais les états de l'automate sont répliqués. La surface du circuit généré est souvent importante.

Cet algorithme a une complexité non polynomiale et est donc lent sur de gros circuit. En effet, un branchement multiplie le nombre de parcours d'exécution par deux et ceci pour chaque branchement!

- Il existe des algorithmes d'ordonnancement très rapides mais qui ne produisent pas de circuits exploitables (surface ou temps de propagation trop grands).

- Il existe des algorithmes d'ordonnancement produisant une solution optimale mais leur complexité n'est pas polynomiale.

- L'ordonnancement est dissocié de l'affectation des opérations fonctionnelles. Or l'affectation détermine les connexions (multiplexeurs, bus) qui influencent considérablement les temps de propagation des opérateurs. Les algorithmes d'ordonnancement n'en tiennent pas compte lorsqu'ils placent les frontières de cycle.

#### 3.2 Les algorithmes d'affectation

L'objectif de l'affectation des opérations est de partager les ressources afin de minimiser la surface. L'affectation est fortement dépendante de l'ordonnancement puisqu'il détermine l'allocation minimale.

On peut utiliser un algorithme général de type *branch and bound* qui explore l'arbre d'exploration des solutions. Chaque noeud est estimé grâce à une fonction de coût globale. Si ce noeud a un coût supérieur à la limite, on peut supprimer ce noeud et tous ses fils de l'arbre d'exploration.

Ces algorithmes ont une complexité non polynomiale. Ce type d'algorithme est utilisé pour l'allocation de ressources [Pan88] [SMT<sup>+</sup>92] mais aussi pour l'ordonnancement [OJ92]. La difficulté de ce type d'algorithme est de trouver la bonne fonction de coût qui permettra une heuristique rapide et réaliste.

Pour la réallocation, on peut aussi utiliser la technique du *recuit simulé* inspirée d'un modèle de simulation physique.

Les affectations des opérations sont permutées tour à tour en conservant ou non les solutions intermédiaires. La solution est conservée suivant son coût et une probabilité autoritaire dont l'influence va décroissante. Au début des permutations, la probabilité est prépondérante sur le coût : des solutions intermédiaires très coûteuses peuvent être conservées. Au fur et à mesure des permutations, la probabilité diminue et le critère de coût devient prépondérant dans la sélection d'une solution.

Cette technique permet de sortir de minimums locaux et d'obtenir une bonne approximation de la solution optimale.

#### 3.2.1 Affectation des opérateurs combinatoires

#### Partitionnement en cliques

Soit G = (N,A) un graphe non orienté avec N un ensemble de noeuds et A un ensemble d'arcs. Une clique est un ensemble de noeuds qui forme sous-graphe complet de G.

La formulation de l'allocation d'opérateurs matériels pour le problème de partitionnement en cliques est :

- chaque opération fonctionnelle est un noeud

- un arc est présent entre deux noeuds (i.e deux opérations) si

- ces deux opérations ne sont pas exécutées dans le même cycle et

- 2. ces deux opérations peuvent s'exécuter sur le même opérateur matériel.

Un noeud peut appartenir à des cliques différentes : une opération fonctionnelle peut être affectée à des opérateurs matériels différents.

Une solution est trouvée lorsque chaque noeud de G appartient à une seule clique : toutes les opérations sont affectées. Le nombre de clique est alors le nombre d'opérateurs matériels.

L'algorithme peut être utilisé pour n'importe quel type de ressource matérielle. [RS91] présente un algorithme d'affectation des registres qui minimise le nombre de registres et prend en compte le coût en surface des interconnexions.

Le problème du partitionnement est donc de trouver le nombre minimal de cliques tel que chaque noeud de *G* appartienne à une seule clique. Le but est de minimiser le nombre d'opérateurs matériels. Ce problème a une complexité non polynomiale. [TS86] a donné une heuristique efficace avec un temps polynômial. Il consiste à privilégier les cliques contenant le plus de noeuds : pour chaque noeud, on ne conserve que les arcs le liant à la plus grosse clique.

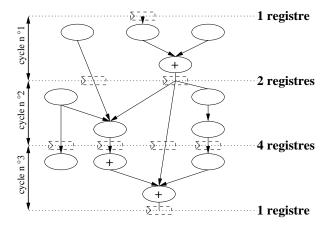

#### 3.2.2 Affectation des registres

#### Left edge

Cet algorithme vient du routage canal d'une vue physique. Il est couramment utilisé pour l'*affectation des registres*. L'une des premières utilisations pour la synthèse est dans [KP87].

Il est basé sur un choix arbitraire pour chaque noeud de l'arbre de décision. L'algorithme se comporte comme suit :

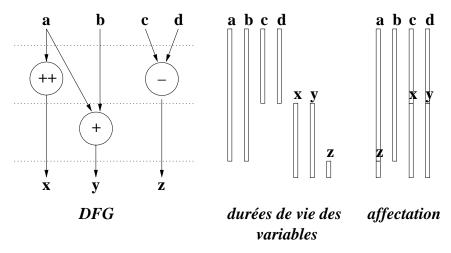

- 1. les valeurs sont triées par ordre d'apparition (naissance) dans le graphe d'ordonnancement. Dans la figure 3.2, la durée de vie des valeurs est modélisée par un *schéma de Gantt*.

- 2. un registre est alloué.

- 3. la liste des valeurs est parcourue dans l'ordre chronologique des naissances : une valeur est affectée au registre si elle n'entre pas en conflit de dates avec les autres valeurs déjà affectées à ce registre.

- 4. Si la liste de valeurs n'est pas vide, il faut repartir à l'étape 2.

FIG. 3.2 Exemple d'application de l'algorithme pour l'affectation des registres.

L'algorithme garantit l'allocation d'un nombre minimum de registres dans un temps très court mais possède deux désavantages :

- l'algorithme n'est pas adapté aux boucles et aux branchements conditionnels car il n'est pas adapté au CDFG. Les durées de vie des variables dépassent la portée des DFG. De plus dans les branchements, les affectations de registres ne sont pas indépendantes.

- l'algorithme ne prend pas en compte le coût des multiplexeurs.

#### Comparaison bipartite par poids

[HCLH90] est une variation de l'algorithme du *left edge*, elle permet d'introduire des poids dans les affectations.

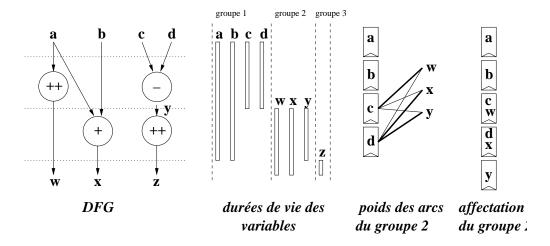

L'algorithme se comporte comme suit :

FIG. 3.3 Exemple d'application de l'algorithme pour l'affectation de registres.

- 1. les valeurs sont triées par ordre d'apparition (naissance) dans le graphe d'ordonnancement (cf. figure 3.3).

- 2. la liste ordonnée des valeurs est scindée en groupes. Un groupe courant est créé. Pour chaque valeur de la liste parcourue :

- Si la valeur est en conflit de dates avec toutes les valeurs du groupe courant, on ajoute cette valeur au groupe courant.

- Sinon on ajoute cette valeur à un nouveau groupe qui devient le groupe courant.

- 3. Pour chaque groupe de la liste ordonnée de valeurs :

- On établit un graphe biparti tel que les noeuds sont les registres et les valeurs appartenant au groupe et les arcs sont positionnés exclusivement entre une valeur et un registre. Un arc existe entre une valeur et un registre si et seulement si cette valeur n'est pas en conflit de date avec les autres valeurs déjà affectées à ce registre. Les arcs possèdent un poids inversement proportionnel à la fonction de coût de l'affectation de la valeur au registre. En général, le poids de l'arc prend en compte les coûts de la connectique (i.e multiplexeurs, bus).

- L'affectation des valeurs est choisie de sorte à favoriser les arcs de poids les plus forts.

**Remarque :** les registres sont alloués au fur et à mesure de l'affectation des valeurs dans les registres. Si une valeur ne peut être affectée dans aucun des registres (conflit de dates), un nouveau registre est alloué.

- L'allocation des registres est dissociée de l'allocation des opérateurs combinatoires. Or ces allocations sont très liées puisqu'elles doivent minimiser les multiplexeurs.

- Les algorithmes d'allocation sont des algorithmes de type glouton qui ne permettent pas d'avoir une vision globale telle que pourrait l'avoir le concepteur.

- L'affectation des registres produit une description de niveau RTL non compréhensible par son concepteur. En effet, les registres ne correspondent pas au variables de la description comportementale. Cela empêche tout ajustement du circuit au niveau RTL.

#### 3.3 Les outils de synthèse haut niveau

Il y a deux types d'outil de synthèse de haut niveau :

- 1. les outils orientés flot de données.

- 2. les outils orientés flot de contrôle ou mixtes.

Les outils orientés flot de contrôle sont en fait des outils mixtes car ils sont capables de traiter des flots de données.

Le concepteur a aussi la possibilité d'utiliser plusieurs outils. Dans [BKV<sup>+</sup>96], Berrebi a utilisé un outil orienté flot de données (*cathedral 2/3* et un outil orienté flot de contrôle (*amical*) pour concevoir un estimateur de mouvement. *amical* a réutilisé le chemin de données généré par *cathedral* pour construire le circuit global. Le circuit généré a été comparé au même circuit conçu "à la main" directement au niveau RTL, le circuit généré de façon automatique est seulement 5 % plus gros.

#### 3.3.1 Outils orientés flot de données

#### **GAUT**

*GAUT* est un outil développé conjointement au Laboratoire d'Analyse des systèmes de Traitement de l'Information (*LASTI*) à Lannion et au Laboratoire d'Etude des Systèmes Temps Réel (*LESTER*).

Cet outil est dédié aux applications de traitement du signal sous contrainte de temps d'exécution [MSDP93]. Il cible principalement la conception sur FPGA (Field Programmable Gate Array) mais peut aussi produire des ASICs (Application Specific Integrated Circuit).

Le circuit généré est un circuit synchrone de niveau RTL (Register Transfer Level) avec une seule horloge.

[?] permet de prendre en compte les contraintes de communication. L'ordonnancement tient alors compte de l'ordre des données échangées avec le système ainsi que des dates auquelles sont possibles ces échanges.

Le concepteur fournit une description comportementale en VHDL [Ins87] du circuit, une bibliothèque de modèles caractérisés, une cadence et une fréquence de fonctionnement. Cette description ne comporte pas d'informations sur les tailles des opérations fonctionnelles car pour les applications visées (de type DSP), les opérations ont généralement toutes la même taille.

La taille des données et des opérations est spécifiée dans la bibliothèque de modèles.

Le concepteur doit caractériser les modèles de la bibliothèque. L'outil utilise les caractéristiques physiques de chaque modèle pour calculer leur coût d'instanciation et respecter les contraintes du concepteur. Ces données caractérisent la surface, les temps de propagation et la consommation de chaque modèle.

Le concepteur doit donc procéder à la synthèse et, éventuellement, au placement/routage de chaque modèle afin d'en extraire les caractéristiques physiques.

Le concepteur fournit à l'outil *GAUT* une cadence et une fréquence de fonctionnement. Ces paramètres constituent le *temps d'exécution total* visé par le concepteur : c'est la contrainte temporelle pour l'algorithme d'ordonnancement. Une fois cette contrainte respectée, la surface et la consommation doivent être minimisées.

Le concepteur peut donner d'autres directives à l'outil comme le choix des fonctions de coût et d'heuristiques. Ces directives interviennent sur de multiples critères tels que l'estimation de la surface, l'algorithme d'affectation des registres, le nombre d'essais et l'affectation des opérateurs combinatoires.

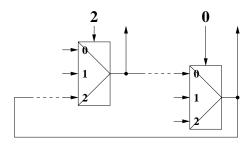

Pour évaluer le nombre de cycles total de la description comportementale, *GAUT* déroule toutes les boucles. Les branchements conditionnels sont cablés, le chemin d'exécution est alors le plus long des deux branchements.

Pour respecter la cadence, l'outil ajoute des opérateurs matériels pour augmenter la parallélisation des opérations fonctionnelles et diminuer le nombre de cycles total d'exécution. L'ordonnancement est basé sur un ASAP avec contrainte temporelle.

Ensuite l'outil détermine l'affectation des registres à chaque cycle à partir de l'ordonnancement.

La construction de l'automate du circuit découle des choix faits lors de l'*ordonnancement*, de l'*affectation* et de la connectique. C'est un automate d'états très simple car il n'y a aucun branchement.